Giới thiệu về Vivado Design Suite

Vivado Design Suite là tổ hợp các phần mềm của hãng Xilinx. Phần mềm này được tạo ra bằng việc nâng cấp các thế hệ phần mềm thiết kế cũ ISE Design Suite. Vivado được dùng để phát triển các ứng dụng trên thế hệ chip và board Xilinx® 7 series, Zynq®-7000 All Programmable, UltraScale™ devices. Các thế hệ board cũ của Xilinx như Series 6 sẽ vẫn được hỗ trợ bởi ISE, Plan Ahead ...

Vivado là phần mềm có rất nhiều chức năng. Nói một cách ngắn gọn, nó hỗ trợ tất cả các khâu của quá trình thiết kế Logic sử dụng FPGA. Các bạn sẽ hiểu cụ thể hơn khả năng của Vivado bằng cách tham khảo thêm về quy trình thiết kế FPGA tại đây.

1. Tạo tài khoản Xilinx:

Trước hết, muốn cài đặt Vivado Design Suite thì bạn cần có 1 tài khoản của Xilinx của riêng mình. Việc đăng ký sẽ hoàn toàn miễn phí, nhanh gọn và dễ dàng. Các bạn tự đăng ký tại đây

2. Tải về phiên bản Vivado Webpack:

Sau khi đăng nhập vào trang chủ của Xilinx, các bạn vào link này để tải về phần mềm.

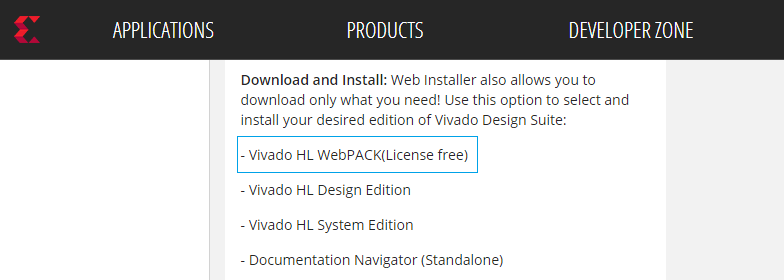

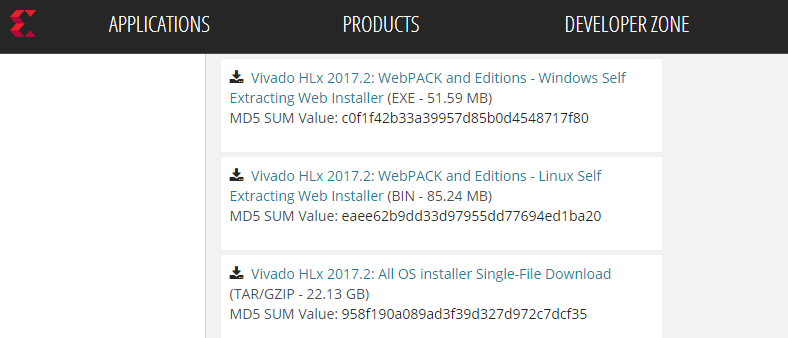

Lưu ý, đây là phần thông tin của phần mềm Vivado phiên bản Webpack ( cài đặt trực tiếp khi có internet ). Các bạn kéo xuống bên dưới 1 chút, sẽ có link tải về cho các phiên bản hệ điều hành tương ứng. Ở hình bên dưới, nếu bạn dùng window thì chọn Link đầu tiên. Click và tải về.

3. Cài đặt

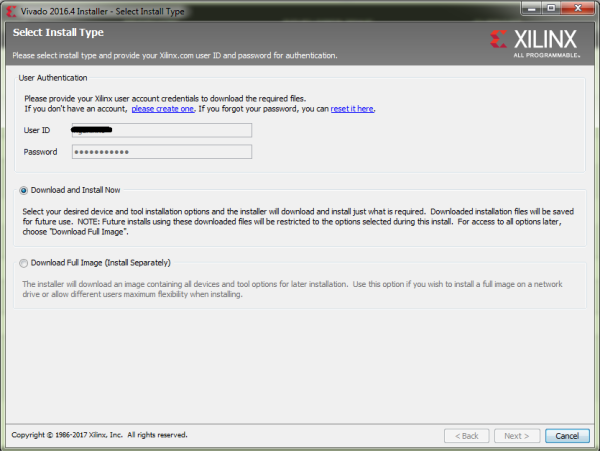

Để tiến hành cài đặt, hãy chạy file mới tải về ở bước 2.

Đầu tiên, Xilinx sẽ yêu cầu bạn đăng nhập account của họ trước khi cho phép bạn cài đặt:

Nhấn Next, sẽ đến cửa sổ bên dưới. Các bạn tích vào Vivado HL WebPACK. Đây là phiên bản phần mềm cài đặt từ web và miễn phí. Phiên bản này có giới hạn một số board FPGA và chip FPGA ( part ). Nhưng đối với nhu cầu của nghiên cứu hoặc các bạn sinh viên thì không cần quan ngại:

Sau khi nhấn Next, các bạn sẽ đến phần xác nhận. Các bạn tích chọn hết để đồng ý với các quy định sử dụng phần mềm:

Kế tiếp, các bạn chọn các phần mềm con trong gói phần mềm Vivado để tải về. Nếu các bạn chỉ làm phần thiết kế phần cứng, chọn như hình dưới. Lưu ý, phần dung lượng tải về sẽ tăng lên, nếu các bạn chọn thêm các tính năng khác để cài đặt.

Đến đây coi như đã xong, các bạn xem lại lựa chọn của mình trước khi nhấn install. Tùy theo nhu cầu mà bạn có thể quay lại để chỉnh sửa cho phù hợp.

Nhấn Install rồi chờ đợi !!

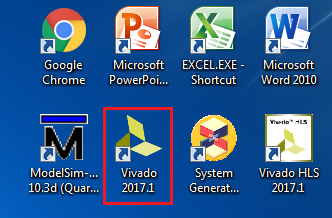

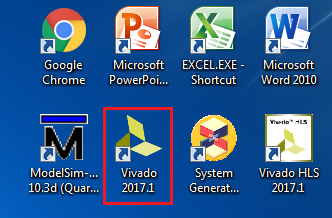

Sau khi cài đặt, bạn có vài Tool đi kèm Vivado ví dụ như, SDK, Vivado HLS, DocNav, System Generator… Bây giờ, các bạn sẽ thao tác với Vivado để xem dạng cấu trúc sơ đồ khối của Verilog code.

4. Mở Vivado và tạo dự án:

Đầu tiên, mở ứng dụng Vivado bằng cách nhấn đúp chuột vào biểu tượng Vivado.

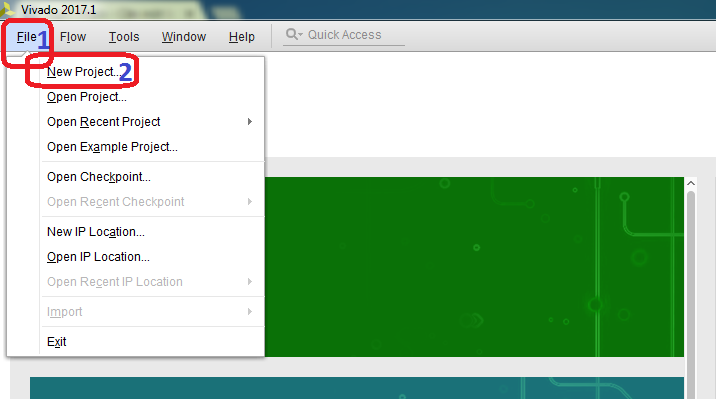

Để tạo dự án mới trên Vivado, các bạn làm như sau:

1 - Chọn File để mở menu chương trình.

2 - Chọn New Project để tạo dự án mới.

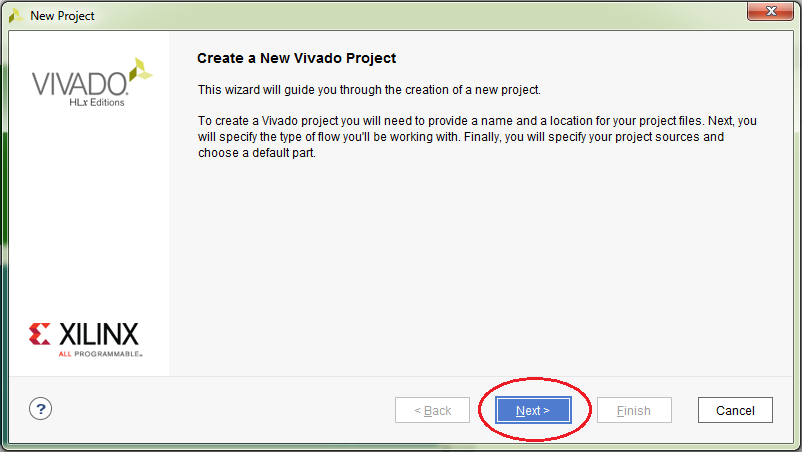

Cửa sổ mới xuất hiện. Bấm Next.

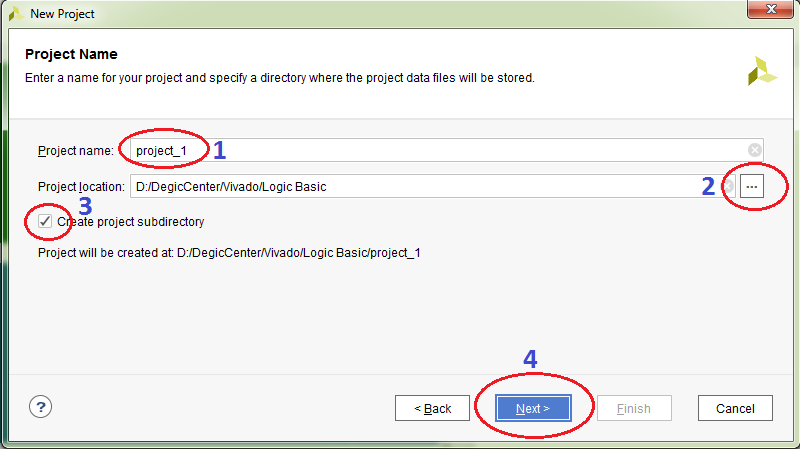

Trên cửa sổ dự án mới, các bạn xác định các thông tin như sau:

1 – Đặt tên cho dự án

2 – Chọn thư mục lưu dự án

3 – Tích chọn vào ô Create project subdirectory ( những thư mục của dự án sẽ tạo bên trong thư mục này )

4 – Bấm Next

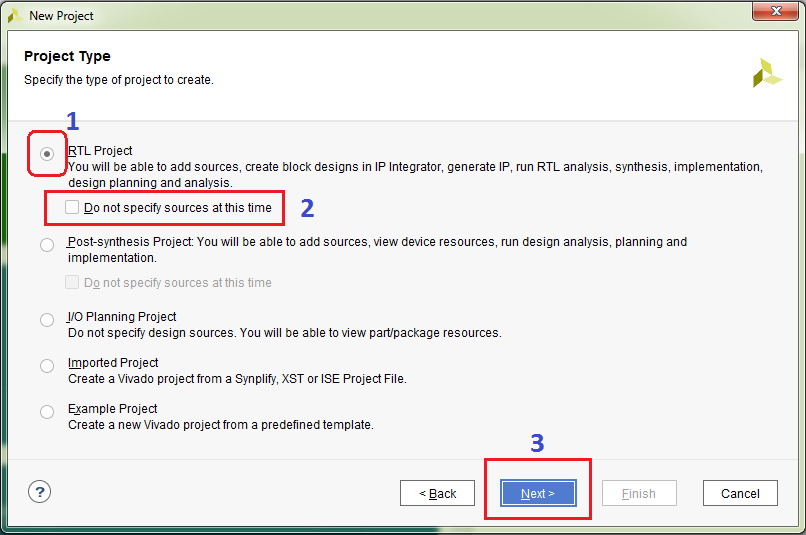

Chọn loại dự án.

1 – Tích chọn ô RTL Project nếu bạn viết code bằng Verilog

2 – Nếu đã có file sẵn và muốn khai báo thì bạn chọn ô này. Nếu muốn thêm file code sau này thì không cần tích chọn.

3 – Bấm Next

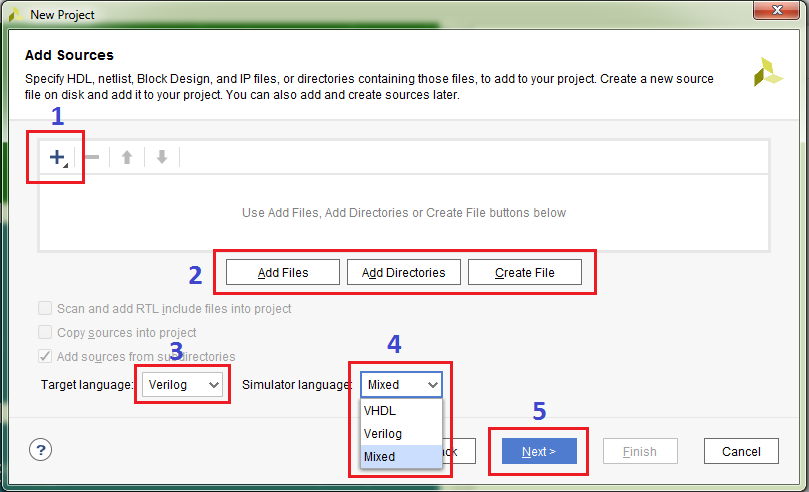

Cửa sổ tiếp theo là Add source. Chúng ta xác định một vài tùy chọn sau đây:

1 – Bấm vào dấu này sẽ ra các tùy chọn như các nút bấm trên dòng số 2

2 – Thêm file code có sẵn – Thêm thư mục – Tạo file code mới

3 – Loại ngôn ngữ bạn muốn dùng. Có 2 loại là Verilog hoặc VHDL

4 – Tùy chọn cho simulator của Vivado. Gồm 3 loại là: VHDL, Verilog và Mixed ( Mixed là dành cho module nào có cả VHDLlẫn Verilog code )

5 – Sau khi chọn file v.v, bấm Next

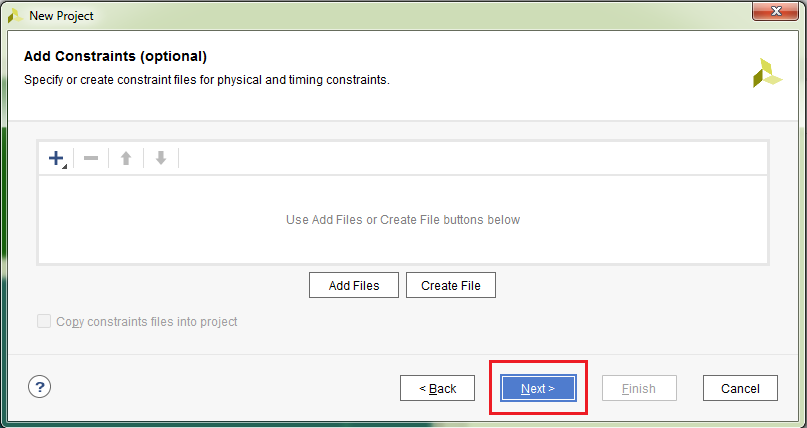

Bước xác định file constraint cho design.

Bước này tạm thời bỏ qua nếu bạn chỉ muốn kiểm tra syntax code và chạy simulation. Bấm Next.

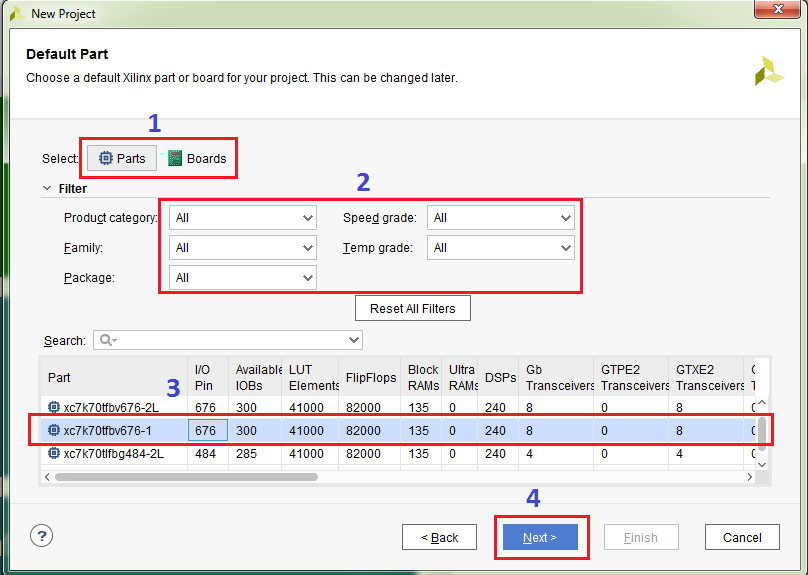

Cửa sổ tiếp theo được dành cho việc chọn loại board/FPGA chip mà bạn nhắm đến.

Mỗi loại Board và chip có số lượng “tài nguyên” tương ứng. Các dự án trong khóa Basic có khối lượng cổng rất thấp, cho nên chọn loại nào cũng được. Tuy nhiên, nếu chọn loại có resource lớn quá hoặc phức tạp quá sẽ làm cho thời gian chạy (runtime ) của dự án lâu hơn. Do đó, các bạn có thể chọn mặc định.

1 – Chọn theo Chip FPGA hoặc Board.

2 – Xác định chip hoặc board theo các thông số, mục đích và các dạng đóng gói.

3 – Đối tượng đang được chọn được highlight màu xanh và các thông số tài nguyên đi kèm.

4 – Bấm Next sau khi chọn xong.

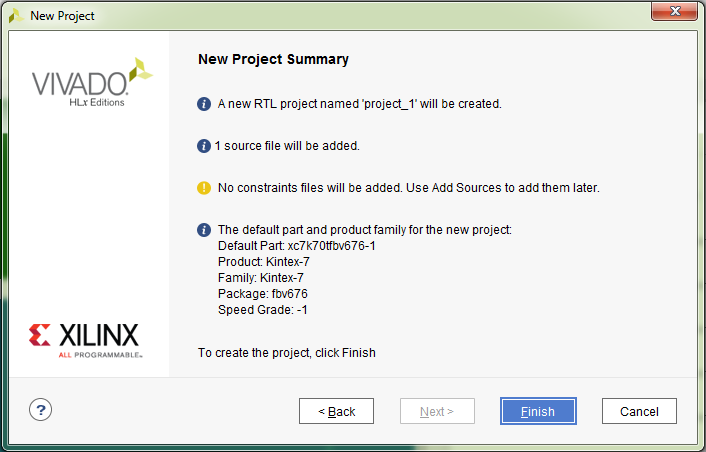

Cửa sổ tiếp theo là thông tin chung của dự án cho đến thời điểm hiện tại.

Nếu bạn thấy ổn, bấm Finish để hoàn tất. Nếu không, bấm Back để quay lại các bước trước đó để điều chỉnh.

Vivado bắt đầu khởi tạo cho dự án:

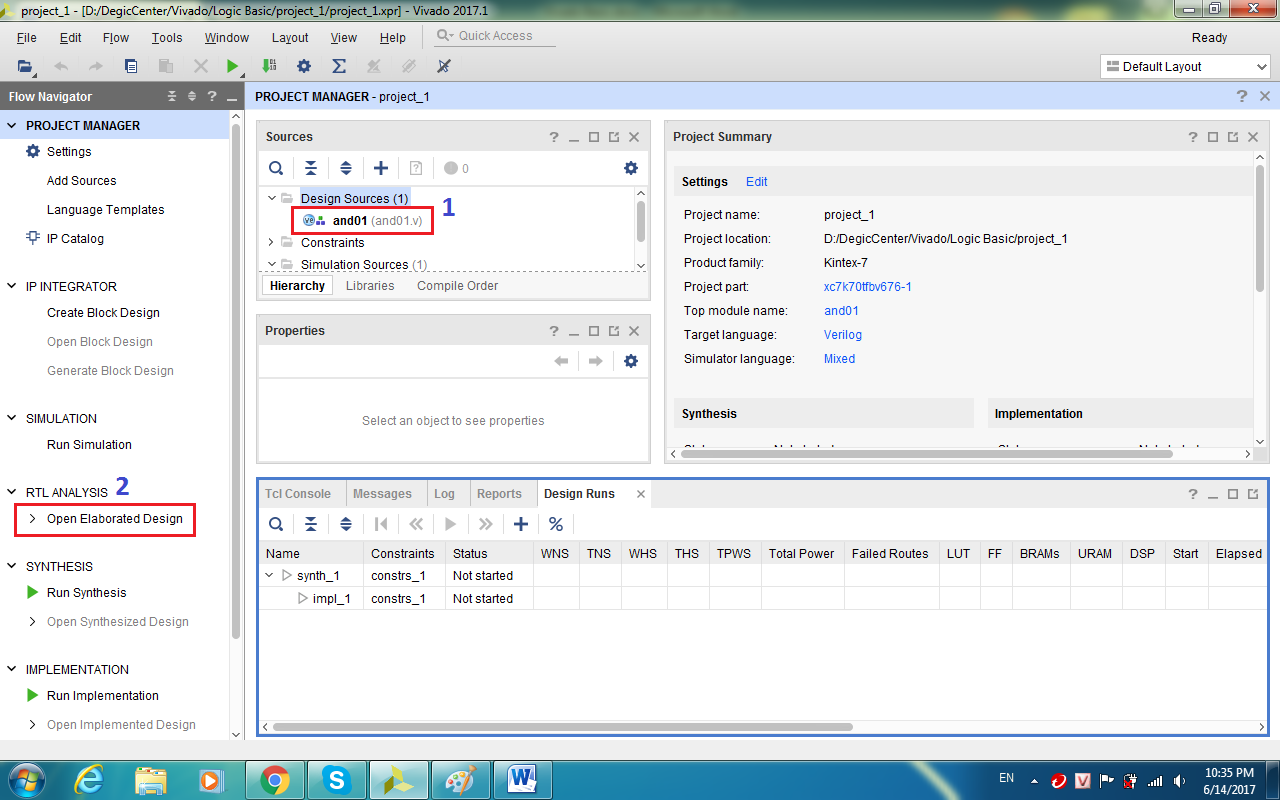

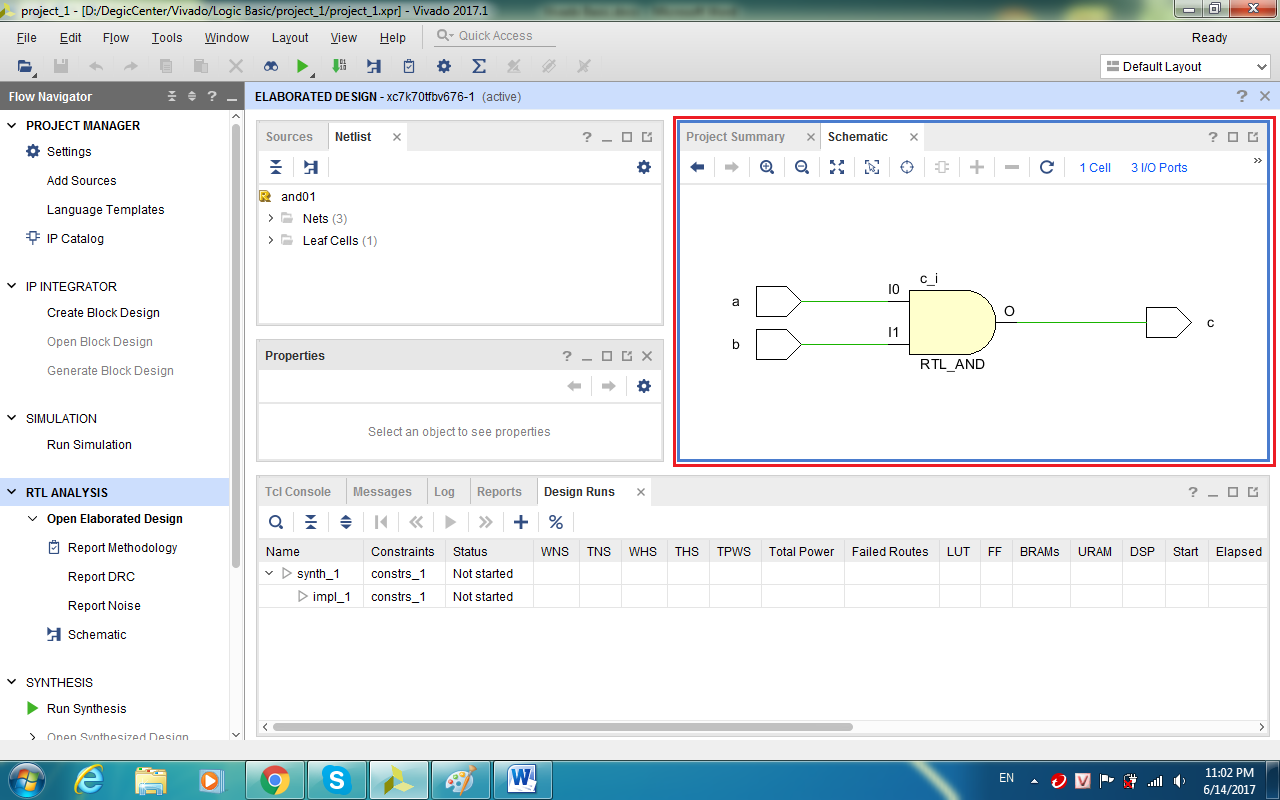

Nếu bạn đã thêm file Verilog code vào thì nó sẽ hiển thị ở (1). Ở mục RTL ANALYSIS, bấm Open Elaborated Design.

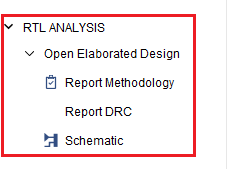

Phần này được mở rộng và các bạn bấm vào Dòng Schematic để coi cấu trúc của Design ở mức RTL. Dạng schematic này giống với Block Diagram ban đầu mà các bạn đã vẽ kèm với dạng sóng của Design.

Đến đây, các bạn đã có thể xem được cấu trúc RTL mà mình viết trên Vivado.

Nguồn: Degic.vn

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)