Design Specification

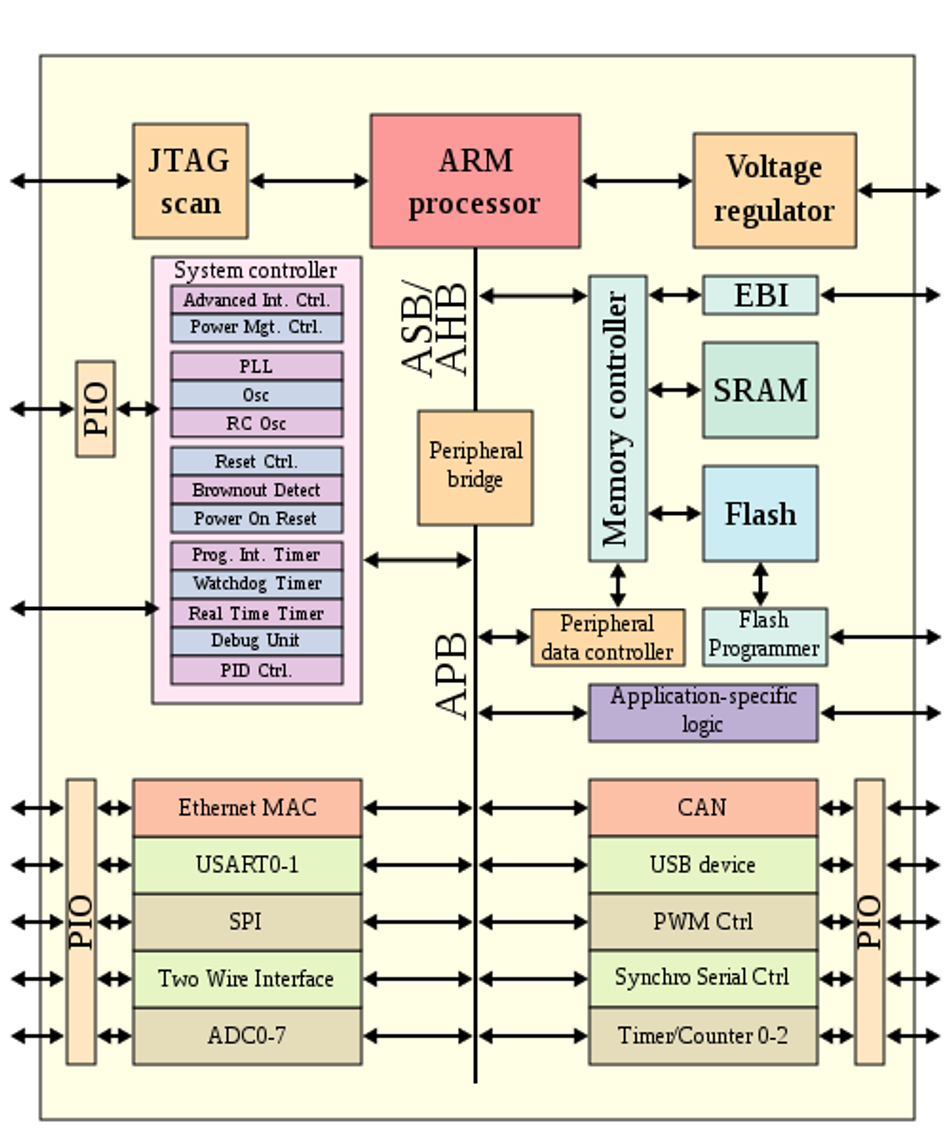

Design Specification A counter having 2 input clocks, clk_a running at 100 MHz and clk_B running at 200MHz.

there are clock divider for clk_A in design. Counter having inputs clk_A , clk_B , reset, count_start1 ,count_start2 and output count_val

1.count_start1 clocking with clk_A

2.count_start2 clocking with clk_B

3.count_val clocking with clk_A

4.reset is synchronous and clocked with clk_A

below is the sample SDC file - counter.sdc

At the top of SDC , below optional commands

# create source clock

create_clock -name clka -period 10 [get_ports clk_A]

create_clock -name clkb -period 5 [get_ports clk_B]

#create generated clock

create_generate_clock -divide_by 2 -source [get_ports clk_A] -name clk_DIV_A [get_pins ]

# set clock uncertainty (setup) , here 10% or more depend on clock frequency and technology library

set_clock_uncertainty -setup [get_clocks clk_A]

set_clock_uncertainty -setup [get_clocks clk_B ]

#set clock uncertainty (hold) , Hold doesn't depend on clock frequency.

# $hold_margin - 50 ps

set_clock_uncertainty -hold $hold_margin [all_clocks]

## set clock latency if required

# declare false path between clk_A and clk_B

set_clock_groups -logically_exclusive [get_clocks clk_A clk_B]

or set_false_path -from clk_A -to clk_B

set_false_path -from clk_B -to clk_A

## Declare input delays and output delays on ports

set_input_delay -clock clk_A -max {0.5*clk_A period} [get_ports count_start1 ]

set_input_delay -clock clk_A min 0 [get_ports count_start1]

set_input_delay -clock clk_B -max {0.5*clk_A period} [get_ports count_start2 ]

set_input_delay -clock clk_B min 0 [get_ports count_start2]

set_output_delay -clock clk_A -max {0.5*clk_A period} [get_ports count_val ]

set_output_delay -clock clk_A min 0 [get_ports count_val]

#declare multicycle paths

set_multicycle_path

##Below are the constraints helps to setup the environments

set_case_analysis 0 [get_pins counter/heir_a/sel_a]

set_driving_cell -lib_cell BUFX9 [all_inputs]

set_fanout_load 8 [all_outputs]

set_load 50 [all_outputs] ## set the value of capacitive load on pin or net in design

# set the specified ports/pins at logic zero or logic one (this is similar to set_case_analysis)

set_logic_zero [get_ports ]

set_logic_one [get_pins ]

set_max_area ## if there is any area specific requirement

set_max_capacitance 0.1 [all_outputs]

set_max_transition 0.2 [all_pins] ## specify the max transition time on pins or ports

set_port_fanout_number 5 [get_ports ] ## set maximum fanout of a port

commands which I have not defined in above sdc -

set_min_delay -from PATH_A -to PATH_B 1 ## set minimum delay 1 ns from path A to B

set_max_delay -from PATH_A -to PATH_B 2 ## set maximum delay 2 ns from path A to B

There are many other commands which may be used in design but those are more specific to the requirement, design implementation , and technology specific. Above all sdc commands are generic commands.

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn