DR SDRAM Controller (SDRC) được thiết kế để sử dụng trong các ứng dụng đòi hỏi băng thông bộ nhớ cao, tốc độ xung nhịp cao và lập trình đầy đủ.

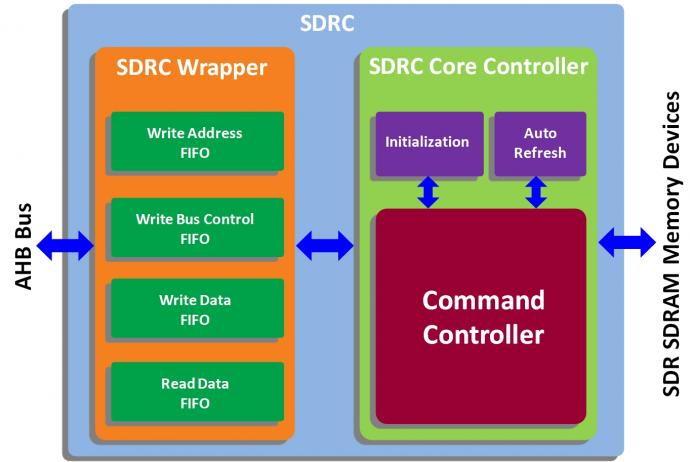

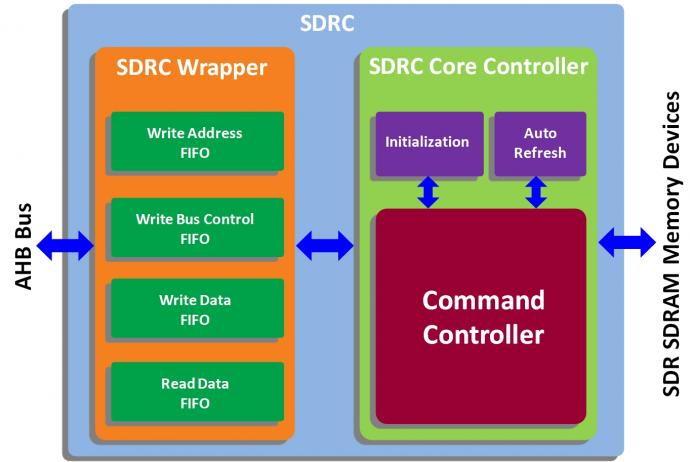

SDRC nhận các lệnh từ bus AMBA 2.0 và chuyển đổi chúng thành chuỗi lệnh được yêu cầu bởi bộ nhớ SDR SDRAM. Ngoài ra, SDRC thực hiện các chức năng: khởi tạo ban đầu hoàn chỉnh, tự động làm tươi, và chế độ tiết kiệm năng lượng (Self Refresh).

SDRC sử dụng kỹ thuật quản lý băng để theo dõi trạng thái của mỗi băng của bộ nhớ SDRAM SDRAM để giảm thời gian truy cập. Hỗ trợ tối đa 8 băng được quản lý đồng thời.

SDRC cung cấp các thông số định thời được cấu hình trước (tCL, tRC, tRCD, tRP, tMRD, tRRD, tRFC, tRAS, tWR) và hỗ trợ nhiều loại burst AHB.

Đặc điểm chính

- Tương thích với bus AMBA AHB

- Cấu hình trước các tham số định thời, mỗi bộ điều khiển được tạo ra cho mỗi loại bộ nhớ SDR SDRAM cụ thể

- Hỗ trợ nhiều tín hiệu chọn chip, có thể điều khiển đồng thời nhiều bộ nhớ SDRAM

- Hỗ trợ hầu hết các loại burst AHB ngoại trừ (WRAP16): SINGLE, INCR, WRAP4, INCR4, WRAP8, INCR8, and INCR16

- Nhận lệnh Load Mode Register (LMR) để lập trình lại bộ nhớ SDRAM trong thời gian đang vận hành

- Hỗ trợ đặc điểm tiết kiệm năng lượng (Self Refresh) cho bộ nhớ

- Hỗ trợ pipeline lệnh SDRAM để đạt hiệu suất vận hành cao

Tần số và tài nguyên

| Tần số | Tài nguyên |

| Cyclone II | 146 MHz | 716 LEs |

Mã nguồn và tài liệu

- Mã nguồn RTL (Verilog HDL)

- Mã nguồn kiểm tra (Verilog HDL)

- Tài liệu sử dụng