1. Giới thiệu về task trong verilog

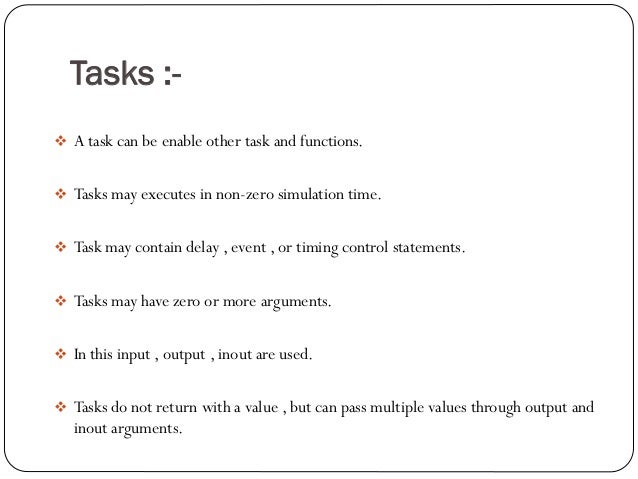

Task được sử dụng trong hầu hết các ngôn ngữ lập trình, chúng được biết đến như là các procecures (thủ tục) hoặc là subroutine (chương trình con).

Task được bắt đầu và kết thúc bằng từ khóa

task

…

endtask

bao gồm các input và output.Một trong những ưu điểm của việt sử dụng task là tránh việc lặp đi lặp lại nhiều đoạn code có cùng một chức năng, thay vào đó, task sẽ được gọi nhiều lần. Ngoài ra, việc sử dụng task giúp cho chương trình có bố cục rõ ràng và dễ hiểu đối với người đọc

2. Một vài nguyên tắc cơ bản khi viết task

– Task được bắt đầu và kết thúc với từ khóa task … endtask

– Các input và output được khai báo sau từ khóa task

– Các biến cục bộ được khai báo sau input và output

3. Ví trị của task

Task được định nghĩa trong module mà chúng được sử dụng. Task cũng có thể được định nghĩa trong một file riêng lẽ và sử dụng từ khóa ‘include để gọi file chứa module mà chúng được sưẻ d ụng

Các biến khai báo trong task là biến cục bộ, chỉ có ý nghĩa trong task. Ngoài ra, thứ tự khai báo trong task (input, output) sẽ tương ứng với thứ tự mà các tham số được truyền vào khi task được gọi.

Task có thể dùng để mô phỏng cả mạch tuần tự và mạch tổ hợp

4. Một vài ví dụ về task trong verilog

module my_first_task();

task sum;

input [3:0] data_in;

output [3:0] data_out;

begin

data_out = data_in + 4'b1010;

end

endtask

endmodule

Task có thể được gọi như sau:

module task_calling (a_in, b_in, c_out, d_out);

input [3:0] a_in, b_in;

output [4:0] c_out, d_out;

reg [3:0] c_out, d_out;

`include "mytask.v"

always @ (a_in)

begin

sum (a_in, c_out);

end

always @ (b_in)

begin

sum (b_in, d_out);

end

endmodule

Task trong test-bench:

module task_calling ();

reg a_in, b_in;

reg c_out, d_out;

initial begin

#0

a_in = 4'b0001;

b_in = 4'b0010;

sum(a_in, c_out);

sum(b_in, d_out);

$display("%4b, %4b, %4b, %4b", a_in, b_in, c_out, d_out);

end

task sum;

input [3:0] data_in;

output [3:0] data_out;

begin

data_out = data_in + 4'b1010;

end

endtask

/*

always @ (a_in) begin sum (a_in, c_out); end always @ (b_in) begin sum (b_in, d_out); end */

endmodule

Nguồn: Tổng hợp

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)