1. Thế nào là thiết kế cho việc kiểm tra

Design For Testability = DFT

DFT là phương pháp dùng trong thiết ASIC bằng cách chèn thêm một số mạch logic vào thiết kế hiện mà không thay đổi đến chức năng của mạch (funtionality). Mục đích của việc chèn mạch logic này phục vụ cho việc kiểm tra thiết kế sau quá trình sản xuất để biết được thiết kế có bị lỗi (defect) trong quá trình sản xuất hay không.

Phương pháp này có ưu điểm là việc kiểm tra có độ bao phủ lớn (coverage) và có thể được cải tiến. Phương pháp này sử dụng các công cụ EDA để tự động tạo ra những bài test và sử dụng các Fault-Model (phương thức xác định mạch logic bị lỗi) để tính độ bao phủ của mạch logic được kiểm tra.

Trong khi đó, đối với phương pháp kiểm tra lỗi bằng chức năng (functionality), các bài test phải được tạo bằng tay bởi người thiết kế và chất lượng của bài test phụ thuộc nhiều vào trình độ của người kĩ sự Thêm vào đó, phương pháp này thông thường có độ bao phủ thấp và rất khó để thống kê được độ bao phủ của các mạch đã test.

2. Giới thiệu về Fault Model

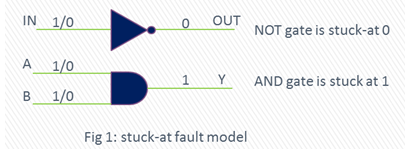

Quan sát hình trên:

a) Cổng NOT luôn luôn output là 0 bất chấp giá trị của input là 0 hay 1. Trong trường hợp này ta nói rằng cổng NOT bị stuck-at 0.

b) Cổng AND luôn luôn output là 1 bất chấp giá trị của input của A và B. Trong trường hợp này ta nói rằng cổng AND bị stuck-at 1.

Stuck-at-1 và stuck-at-0 chính là các loại mô hình lỗi (fault model)

Bạn có đam mê ngành thiết kế vi mạch và bạn muốn có mức lương 1000 usd cùng lúc bạn