1. Các quy tắc trong thiết kế vi mạch (Design Rule Checks)

1. Các quy tắc trong thiết kế vi mạch (Design Rule Checks)

Ở mỗi công đoạn trong thiết kế vi mạch, các quy tắc thiết kế được đưa ra nhằm đảo bảo tính đúng đắn của thiết kế, đồng thời để đạt được tỉ lệ yield cao nhất (tỉ lệ chip sản xuất không bị lỗi). Ngoài ra, trong một chuổi các công đoạn trong quy trình thiết kế, dữ liệu đầu ra của một công đoạn chính là dữ liệu đầu vào của một công đoạn khác. Do đó, các dữ đầu ra (output) của mỗi công đoạn, phải đảm bảo tuân thủ các quy tắc của công đoạn tiếp theo.

Ví dụ ở thiết kế Front-end, trong bước thiết kế RTL, các quy tắc được đưa ra nhằm đảm bảo RTL có thể thiết kế để tổng hợp được (synthesizable).

Hoặc trong quá trình thiết kế layout vật lý, các quy tắc được đưa ra để đảm bảo dữ liệu có thể được ra mask và sản xuất với tỉ lệ thành công cao.

Các quy tắc thiết kế này được đưa ra bởi từng công ty thiết kế chip, hoặc được đưa ra bởi những nhà sản xuất chip và các công ty thiết kế phải tuân thủ theo.

thegioivimach.com xin giới thiệu quy tắc thiết kế ở mức Front-end và quy tắc thiết kế ở mức Back-end như sau:

2. Logical Design Rule Check (RTL Checker)

Các quy tắc cơ bản khi thiết kế RTL code

– Đảm bảo tính đúng đắn về mặt logic:

– Có thể tổng hợp được (synthesize-able)

– Có thể thực hiện việc chèn mạch để test được

– Có thể làm STA được

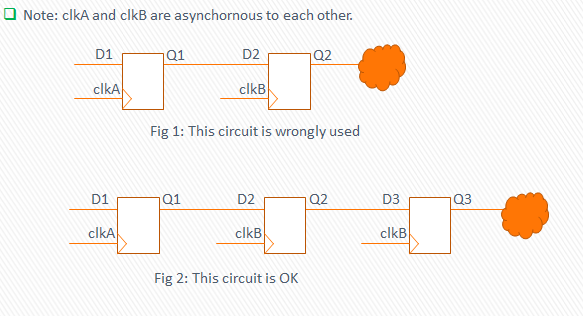

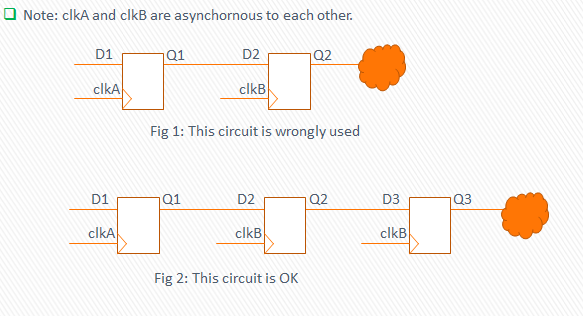

Ví dụ về quy tắc thiết kế RTL khi đồng một tín hiệu đi từ miền clock clkA sang miền clock clkB. Trong đó, clkA và clkB là hai clock bất đồng bộ.

3. Các công cụ kiểm tra quy tắc thiết kế RTL (RTL Design Rule Check)

Một trong những công cụ phổ biến nhất được sử dụng để kiểm tra tính là Spyglass của Atrenta.

Bạn có đam mê ngành thiết kế vi mạch và bạn muốn có mức lương 1000 usd cùng lúc bạn