# 14-Bit PWM Timer (PWM)

This LSI has an on-chip 14-bit pulse-width modulator (PWM) timer with four output channels. It can be connected to an external low-pass filter to operate as a 14-bit D/A converter.

### 10.1 Features

Division of pulse into multiple base cycles to reduce ripple Eight resolution settings

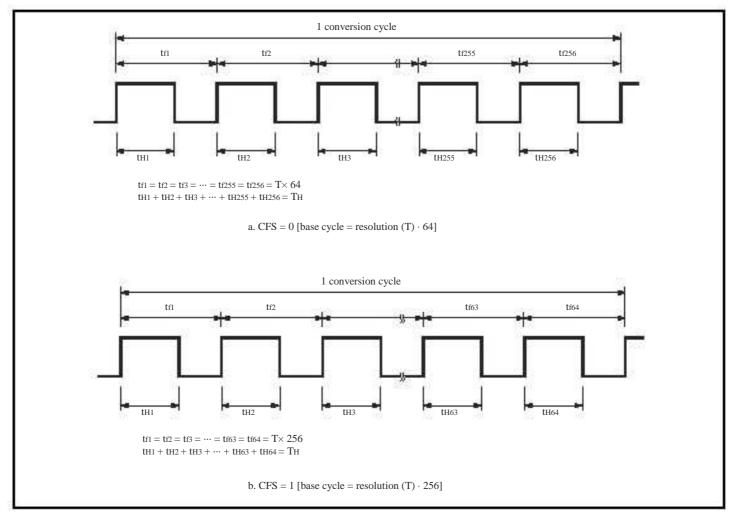

The resolution can be set to 1, 2, 64, 128, 256, 1024, 4096, or 16384 system clock cycles. Two base cycle settings

The base cycle can be set equal to  $T \cdot 64$  or  $T \cdot 256$ , where T is the resolution.

Sixteen operation clocks (by combination of eight resolution settings and two base cycle settings)

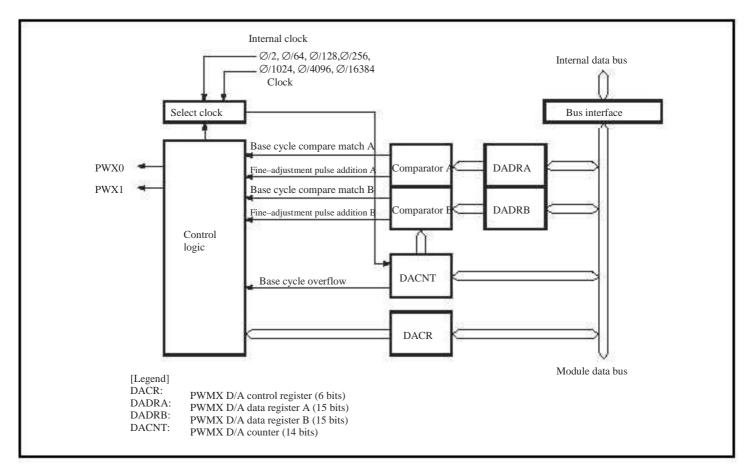

Figure 10.1 shows a block diagram of the PWM (D/A) module.

### **10.2** Input/Output Pins

Table 10.1 lists the PWMX (D/A) module input and output pins.

#### Table 10.1 Pin Configuration

| Name              | Abbreviation I/O |        | Function                                   |

|-------------------|------------------|--------|--------------------------------------------|

| PWMX output pin 0 | PWX0             | Output | PWM timer pulse output of PWMX_0 channel A |

| PWMX output pin 1 | PWX1             | Output | PWM timer pulse output of PWMX_0 channel B |

| PWMX output pin 2 | PWX2             | Output | PWM timer pulse output of PWMX_1 channel A |

| PWMX output pin 3 | PWX3             | Output | PWM timer pulse output of PWMX_1 channel B |

## **10.3** Register Descriptions

The PWMX (D/A) module has the following registers. The PWMX (D/A) registers are assigned to the same addresses with other registers. The registers are selected by the IICE bit in the serial timer control register (STCR). For details on the module stop control register, see section 23.1.3, Module Stop Control Register H, L, and A (MSTPCRH, MSTPCRL, MSTPCRA).

PWMX (D/A) counter (DACNT) PWMX (D/A) data register A (DADRA)

PWMX (D/A) data register B (DADRB)

PWMX (D/A) control register (DACR)

Peripheral clock select register (PCSR)

Note: The same addresses are shared by DADRA and DACR, and by DADRB and DACNT. Switching is performed by the REGS bit in DACNT or DADRB.

#### 10.3.1 PWMX (D/A) Counter (DACNT)

DACNT is a 14-bit readable/writable up-counter. The input clock is selected by the clock select bit (CKS) in DACR. DACNT functions as the time base for both PWMX (D/A) channels. When a channel operates with 14-bit precision, it uses all DACNT bits. When a channel operates with 12-bit precision, it uses the lower 12 bits and ignores the upper two bits. DACNT cannot be accessed in 8-bit units. DACNT should always be accessed in 16-bit units. For details, see section 10.4, Bus Master Interface.

| Bit     | Bit Name      | Initial<br>Value | R/W | Description                                                                                                                                                                                                  |

|---------|---------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 8 | UC7 to UC0    | All 0            | R/W | Lower Up-Counter                                                                                                                                                                                             |

| 7 to 2  | UC8 to UC13 A | .11 0            | R/W | Upper Up-Counter                                                                                                                                                                                             |

| 1       |               | 1                | R   | Reserved                                                                                                                                                                                                     |

|         |               |                  |     | This bit is always read as 1 and cannot be modified.                                                                                                                                                         |

| 0       | REGS          | 1                | R/W | Register Select                                                                                                                                                                                              |

|         |               |                  |     | DADRA and DACR, and DADRB and DACNT, are<br>located at the same addresses. The REGS bit specifies<br>which registers can be accessed. When changing the<br>register to be accessed, set this bit in advance. |

|         |               |                  |     | 0: DADRA and DADRB can be accessed                                                                                                                                                                           |

|         |               |                  |     | 1: DACR and DACNT can be accessed                                                                                                                                                                            |

| -       |               |                  |     |                                                                                                                                                                                                              |

#### DACNT

### 10.3.2 PWMX (D/A) Data Registers A and B (DADRA and DADRB)

DADRA corresponds to PWMX (D/A) channel A, and DADRB to PWMX (D/A) channel B. The DADR registers cannot be accessed in 8-bit units. The DADR registers should always be accessed in 16-bit units. For details, see section 10.4, Bus Master Interface.

DADRA

| Bit     | Bit Name    | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|-------------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 2 | DA13 to DA0 | All 1            | R/W | D/A Data 13 to 0                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |             |                  |     | These bits set a digital value to be converted to an analog value.                                                                                                                                                                                                                                                                                                                                                           |

|         |             |                  |     | In each base cycle, the DACNT value is continually<br>compared with the DADR value to determine the duty<br>cycle of the output waveform, and to decide whether to<br>output a fine-adjustment pulse equal in width to the<br>resolution. To enable this operation, this register must<br>be set within a range that depends on the CFS bit. If the<br>DADR value is outside this range, the PWM output is<br>held constant. |

|         |             |                  |     | A channel can be operated with 12-bit precision by fixing DA0 and DA1 to 0. The two data bits are not compared with UC12 and UC13 of DACNT.                                                                                                                                                                                                                                                                                  |

| 1       | CFS         | 1                | R/W | Carrier Frequency Select                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |             |                  |     | 0: Base cycle = resolution (T) $\cdot$ 64<br>The range of DA13 to DA0: H'0100 to H'3FFF                                                                                                                                                                                                                                                                                                                                      |

| 8       |             |                  |     | 1: Base cycle = resolution (T) $\cdot$ 256<br>The range of DA13 to DA0: H'0040 to H'3FFF                                                                                                                                                                                                                                                                                                                                     |

| 0       |             | 1                | R   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |             |                  |     | This bit is always read as 1 and cannot be modified.                                                                                                                                                                                                                                                                                                                                                                         |

### DADRB

| Bit     | Bit Name          | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|-------------------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 2 | DA13 to DA0 All 1 |                  | R/W | D/A Data 13 to 0                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |                   |                  |     | These bits set a digital value to be converted to an analog value.                                                                                                                                                                                                                                                                                                                                                           |

|         |                   |                  |     | In each base cycle, the DACNT value is continually<br>compared with the DADR value to determine the duty<br>cycle of the output waveform, and to decide whether to<br>output a fine-adjustment pulse equal in width to the<br>resolution. To enable this operation, this register must<br>be set within a range that depends on the CFS bit. If the<br>DADR value is outside this range, the PWM output is<br>held constant. |

|         |                   |                  |     | A channel can be operated with 12-bit precision by fixing DA0 and DA1 to 0. The two data bits are not compared with UC12 and UC13 of DACNT.                                                                                                                                                                                                                                                                                  |

| 1       | CFS               | 1                | R/W | Carrier Frequency Select                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                   |                  |     | 0: Base cycle = resolution (T) $\cdot$ 64<br>DA13 to DA0 range = H'0100 to H'3FFF                                                                                                                                                                                                                                                                                                                                            |

|         |                   |                  |     | 1: Base cycle = resolution (T) $\cdot$ 256<br>DA13 to DA0 range = H'0040 to H'3FFF                                                                                                                                                                                                                                                                                                                                           |

| )       | REGS              | 1                | R/W | Register Select                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |                   |                  |     | DADRA and DACR, and DADRB and DACNT, are<br>located at the same addresses. The REGS bit specifies<br>which registers can be accessed. When changing the<br>register to be accessed, set this bit in advance.                                                                                                                                                                                                                 |

|         |                   |                  |     | 0: DADRA and DADRB can be accessed                                                                                                                                                                                                                                                                                                                                                                                           |

|         |                   |                  |     | 1: DACR and DACNT can be accessed                                                                                                                                                                                                                                                                                                                                                                                            |

# 10.3.3 PWMX (D/A) Control Register (DACR)

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                           |

|-----|----------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   |          | 0             | R/W | Reserved                                                                                                                                              |

|     |          |               |     | The initial value should not be changed.                                                                                                              |

| 6   | PWME     | 0             | R/W | PWMX Enable                                                                                                                                           |

|     |          |               |     | Starts or stops the PWM D/A counter (DACNT).                                                                                                          |

|     |          |               |     | 0: DACNT operates as a 14-bit up-counter                                                                                                              |

|     |          |               |     | 1: DACNT halts at H'0003                                                                                                                              |

| 5,4 |          | All 1         | R   | Reserved                                                                                                                                              |

|     |          |               |     | These bits are always read as 1 and cannot be modified.                                                                                               |

| 3   | OEB      | 0             | R/W | Output Enable B                                                                                                                                       |

|     |          |               |     | Enables or disables output on PWMX (D/A) channel B.                                                                                                   |

|     |          |               |     | 0: PWMX (D/A) channel B output (at the PWX1, PWX3 pins) is disabled                                                                                   |

|     |          |               |     | 1: PWMX (D/A) channel B output (at the PWX1, PWX3 pins) is enabled                                                                                    |

| 2   | OEA      | 0             | R/W | Output Enable A                                                                                                                                       |

|     |          |               |     | Enables or disables output on PWMX (D/A) channel A.                                                                                                   |

|     |          |               |     | 0: PWMX (D/A) channel A output (at the PWX0, PWX2 pin) is disabled                                                                                    |

|     |          |               |     | 1: PWMX (D/A) channel A output (at the PWX0, PWX2 pins) is enabled                                                                                    |

| 1   | OS       | 0             | R/W | Output Select                                                                                                                                         |

|     |          |               |     | Selects the phase of the PWMX (D/A) output.                                                                                                           |

|     |          |               |     | 0: Direct PWMX (D/A) output                                                                                                                           |

|     |          |               |     | 1: Inverted PWMX (D/A) output                                                                                                                         |

| 0   | CKS      | 0             | R/W | Clock Select                                                                                                                                          |

|     |          |               |     | Selects the PWMX (D/A) resolution. Eight kinds of resolution can be selected.                                                                         |

|     |          |               |     | 0: Operates at resolution (T) = system clock cycle time<br>(t <sub>cyc</sub> )                                                                        |

|     |          |               |     | 1: Operates at resolution (T) = system clock cycle time $(t_{cyc}) \cdot 2, \cdot 64, \cdot 128, \cdot 256, \cdot 1024, \cdot 4096, and \cdot 16384.$ |

DACR enables the PWM outputs, and selects the output phase and operating speed.

# **10.3.4** Peripheral Clock Select Register (PCSR)

| Bit | Bit Name | Initial Value | R/W | Description                                                                 |

|-----|----------|---------------|-----|-----------------------------------------------------------------------------|

| 7   | PWCKX1B  | 0             | R/W | PWMX_1 Clock Select                                                         |

| 6   | PWCKX1A  | 0             | R/W | These bits select a clock cycle with the CKS bit of DACR of PWMX_1 being 1. |

|     |          |               |     | See table 10.2.                                                             |

| 5   | PWCKX0B  | 0             | R/W | PWMX_0 Clock Select                                                         |

| 4   | PWCKX0A  | 0             | R/W | These bits select a clock cycle with the CKS bit of DACR of PWMX_0 being 1. |

|     |          |               |     | See table 10.2.                                                             |

| 3   | PWCKX1C  | 0             | R/W | PWMX_1 Clock Select                                                         |

|     |          |               |     | This bit selects a clock cycle with the CKS bit of DACR of PWMX_1 being 1.  |

|     |          |               |     | See table 10.2.                                                             |

| 2   | PWCKB    | 0             | R/W | PWM Clock Select B and A                                                    |

| 1   | PWCKA    | 0             | R/W | See section 9.3.5, Peripheral Clock Select Register (PCSR).                 |

| 0   | PWCKX0C  | 0             | R/W | PWMX_0 Clock Select                                                         |

|     |          |               |     | This bit selects a clock cycle with the CKS bit of DACR of PWMX_0 being 1.  |

|     |          |               |     | See table 10.2.                                                             |

PCSR and the CKS bit of DACR select the operating speed.

# Table 10.2 Clock Select of PWMX\_1 and PWMX\_0

| PWCKX0C<br>PWCKX1C | PWCKX0B<br>PWCKX1B | PWCKX0A<br>PWCKX1A | Resolution (T)                                          |

|--------------------|--------------------|--------------------|---------------------------------------------------------|

| 0                  | 0                  | 0                  | Operates on the system clock cycle $(t_{cyc}) \ge 2$    |

| 0                  | 0                  | 1                  | Operates on the system clock cycle $(t_{cyc}) \ge 64$   |

| 0                  | 1                  | 0                  | Operates on the system clock cycle $(t_{cyc}) \ge 128$  |

| 0                  | 1                  | 1                  | Operates on the system clock cycle $(t_{cyc}) \ge 256$  |

| 1                  | 0                  | 0                  | Operates on the system clock cycle $(t_{cyc}) \ge 1024$ |

| 1                  | 0                  | 1                  | Operates on the system clock cycle $(t_{cyc}) \ge 4096$ |

| 1                  | 1                  | 0                  | Operates on the system clock cycle $(t_{cyc})$ x 16384  |

| 1                  | 1                  | 1                  | Setting prohibited                                      |

|                    |                    |                    |                                                         |

### **10.4 Bus Master Interface**

DACNT, DADRA, and DADRB are 16-bit registers. The data bus linking the bus master and the on-chip peripheral modules, however, is only 8 bits wide. When the bus master accesses these registers, it therefore uses an 8-bit temporary register (TEMP).

These registers are written to and read from as follows.

#### Write

When the upper byte is written to, the upper-byte write data is stored in TEMP. Next, when the lower byte is written to, the lower-byte write data and TEMP value are combined, and the combined 16-bit value is written in the register.

Read

When the upper byte is read from, the upper-byte value is transferred to the CPU and the lower-byte value is transferred to TEMP. Next, when the lower byte is read from, the lower-byte value in TEMP is transferred to the CPU.

These registers should always be accessed 16 bits at a time with a MOV instruction, and the upper byte should always be accessed before the lower byte. Correct data will not be transferred if only the upper byte or only the lower byte is accessed. Also note that a bit manipulation instruction cannot be used to access these registers.

#### Example 1: Write to DACNT

MOV.W R0, @DACNT ; Write R0 contents to DACNT

#### Example 2: Read DADRA

MOV.W @DADRA, R0 ; Copy contents of DADRA to R0

## 10.5 Operation

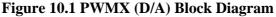

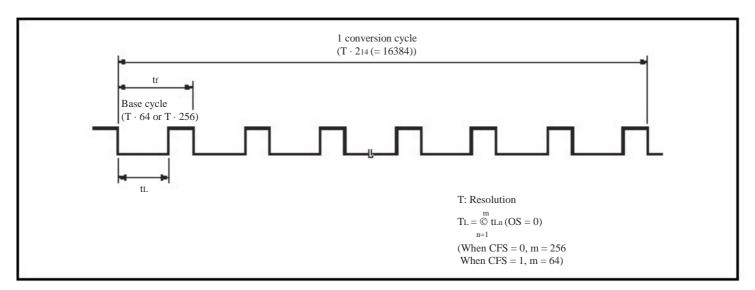

A PWM waveform like the one shown in figure 10.2 is output from the PWX pin. DA13 to DA0 in DADR corresponds to the total width ( $T_L$ ) of the low (0) pulses output in one conversion cycle (256 pulses when CFS = 0, 64 pulses when CFS = 1). When OS = 0, this waveform is directly output. When OS = 1, the output waveform is inverted, and DA13 to DA0 in DADR value corresponds to the total width ( $T_H$ ) of the high (1) output pulses. Figures 10.3 and 10.4 show the types of waveform output available.

Figure 10.2 PWMX (D/A) Operation

Table 10.3 summarizes the relationships between the CKS and CFS bit settings and the resolution, base cycle, and conversion cycle. The PWM output remains fixed unless DA13 to DA0 in DADR contain at least a certain minimum value. The relationship between the OS bit and the output waveform is shown in figures 10.3 and 10.4.

|   | PCS        | R |     |                      |     |           |                 |                                                      | Fix      | ed DAD | R Bits |        |       | _             |

|---|------------|---|-----|----------------------|-----|-----------|-----------------|------------------------------------------------------|----------|--------|--------|--------|-------|---------------|

|   | CKX<br>CKX |   | _   | Reso-<br>lution<br>T |     | Base      | Conver-<br>sion | TL/TH                                                | Accuracy |        |        | t Data |       | Conversion    |

| С | В          | А | CKS | (µs)                 | CFS | Cycle     | Cycle           | (OS = 0/OS = 1)                                      | (Bits)   | I      | DA3    | DA2 I  | DA1 D | AQCycle (ms)* |

|   |            |   | 0   | 0.03                 | 0   | 1.94      | 496.48          | Always low/high output                               | 14       |        |        |        |       | 0.50          |

|   |            |   |     |                      |     | (µs)      | (µs)            | DA13 to $0 = H'0000$ to H'00FF<br>(Data value) · T   | 12       |        |        | 0      | 0     | 0.12          |

|   |            |   |     |                      |     | /515.6kHz |                 | DA13 to $0 = H'0100$ to H'3FFF                       | 10       | 0      | 0      | 0      | 0     | 0.03          |

|   |            |   |     |                      | 1   | 7.76      | 496.48          | Always low/high output                               | 14       |        |        |        |       | 0.50          |

|   |            |   |     |                      |     | (µs)      | (µs)            | DA13 to $0 = H'0000$ to $H'003F$<br>(Data value) · T | 12       |        |        | 0      | 0     | 0.12          |

|   |            |   |     | (φ)                  |     | /128.9kHz |                 | DA13 to $0 =$ H'0040 to H'3FFF                       | 10       | 0      | 0      | 0      | 0     | 0.03          |

| ) | 0          | 0 | 1   | 0.06                 | 0   | 3.88      | 0.99            | Always low/high output                               | 14       |        |        |        |       | 0.99          |

|   |            |   |     |                      |     | (µs)      | (ms)            | DA13 to $0 =$ H'0000 to H'00FF<br>(Data value) · T   | 12       |        |        | 0      | 0     | 0.25          |

|   |            |   |     |                      |     | /257.8kHz |                 | DA13 to $0 =$ H'0100 to H'3FFF                       | 10       | 0      | 0      | 0      | 0     | 0.06          |

|   |            |   |     |                      | 1   | 15.52     | 0.99            | Always low/high output                               | 14       |        |        |        |       | 0.99          |

|   |            |   |     |                      |     | (µs)      | (ms)            | DA13 to $0 = H'0000$ to $H'003F$<br>(Data value) · T | 12       |        |        | 0      | 0     | 0.25          |

|   |            |   |     | (φ/2)                |     | /64.5kHz  |                 | DA13 to $0 =$ H'0040 to H'3FFF                       | 10       | 0      | 0      | 0      | 0     | 0.06          |

| ) | 0          | 1 | 1   | 1.94                 | 0   | 124.12    | 31.78           | Always low/high output                               | 14       |        |        |        |       | 31.78         |

|   |            |   |     |                      |     | (µs)      | (ms)            | DA13 to $0 =$ H'0000 to H'00FF<br>(Data value) · T   | 12       |        |        | 0      | 0     | 7.94          |

|   |            |   |     |                      |     | /8.1kHz   |                 | DA13 to $0 =$ H'0100 to H'3FFF                       | 10       | 0      | 0      | 0      | 0     | 1.99          |

|   |            |   |     |                      | 1   | 496.48    | 31.78           | Always low/high output                               | 14       |        |        |        |       | 31.78         |

|   |            |   |     |                      |     | (µs)      | (ms)            | DA13 to $0 = H'0000$ to $H'003F$<br>(Data value) · T | 12       |        |        | 0      | 0     | 7.94          |

|   |            |   |     | (φ/64)               |     | /2.0kHz   |                 | DA13 to $0 =$ H'0040 to H'3FFF                       | 10       | 0      | 0      | 0      | 0     | 1.99          |

| ) | 1          | 0 | 1   | 3.88                 | 0   | 248.24    | 63.55           | Always low/high output                               | 14       |        |        |        |       | 63.55         |

|   |            |   |     |                      |     | (µs)      | (ms)            | DA13 to $0 =$ H'0000 to H'00FF<br>(Data value) · T   | 12       |        |        | 0      | 0     | 15.89         |

|   |            |   |     |                      |     | /4.0kHz   |                 | DA13 to $0 =$ H'0100 to H'3FFF                       | 10       | 0      | 0      | 0      | 0     | 3.97          |

|   |            |   |     |                      | 1   | 992.97    | 63.55           | Always low/high output                               | 14       |        |        |        |       | 63.55         |

|   |            |   |     |                      |     | (µs)      | (ms)            | DA13 to $0 = H'0000$ to $H'003F$<br>(Data value) · T | 12       |        |        | 0      | 0     | 15.89         |

|   |            |   |     | (φ/128)              |     | /1.0kHz   |                 | DA13 to $0 = H'0040$ to H'3FFF                       | 10       | 0      | 0      | 0      | 0     | 3.97          |

# Table 10.3 Settings and Operation (Examples when ) = 33 MHz)

|   | 1 0.01     |   |     |                       |     |          |                 |                                                            |          |   |       |       |       | -            |

|---|------------|---|-----|-----------------------|-----|----------|-----------------|------------------------------------------------------------|----------|---|-------|-------|-------|--------------|

|   | CKX<br>CKX |   |     | Reso-<br>lution<br>T  |     | Base     | Conver-<br>sion | TL/TH                                                      | Accuracy | 8 | Bit   | Data  |       | Conversion   |

| ! | B          | A | CKS | (µs)                  | CFS | Cycle    | Cycle           | (OS = 0/OS = 1)                                            | (Bits)   | Γ | DA3 I | DA2 I | DA1 D | ACycle (ms)* |

|   | 1          | 1 | 1   | 7.76                  | 0   | 496.48   | 127.10          | Always low/high output                                     | 14       |   |       |       |       | 127.10       |

|   |            |   |     |                       |     | (µs)     | (ms)            | DA13 to $0 = H'0000$ to H'00FF<br>(Data value) $\cdot$ T   | 12       |   |       | 0     | 0     | 31.78        |

|   |            |   |     |                       |     | /2.0kHz  |                 | DA13 to $0 = H'0100$ to H'3FFF                             | 10       | 0 | 0     | 0     | 0     | 7.94         |

|   |            |   |     |                       | 1   | 1985.94  | 127.10          | Always low/high output                                     | 14       |   |       |       |       | 127.10       |

|   |            |   |     |                       |     | (µs)     | (ms)            | DA13 to $0 = H'0000$ to $H'003F$<br>(Data value) $\cdot T$ | 12       |   |       | 0     | 0     | 31.78        |

|   |            |   |     | (φ/256)               |     | /0.5kHz  |                 | DA13 to $0 = H'0040$ to H'3FFF                             | 10       | 0 | 0     | 0     | 0     | 7.94         |

|   | 0          | 0 | 1   | 31.03                 | 0   | 1.99     | 508.40          | Always low/high output                                     | 14       |   |       |       |       | 508.40       |

|   |            |   |     |                       |     | (ms)     | (ms)            | DA13 to $0 = H'0000$ to $H'00FF$<br>(Data value) $\cdot T$ | 12       |   |       | 0     | 0     | 127.10       |

|   |            |   |     |                       |     | /503.5Hz |                 | DA13 to $0 = H'0100$ to H'3FFF                             | 10       | 0 | 0     | 0     | 0     | 31.78        |

|   |            |   |     |                       | 1   | 7.94     | 508.40          | Always low/high output                                     | 14       |   |       |       |       | 508.40       |

|   |            |   |     |                       |     | (ms)     | (ms)            | DA13 to $0 = H'0000$ to $H'003F$<br>(Data value) $\cdot T$ | 12       |   |       | 0     | 0     | 127.10       |

|   |            |   |     | (φ/1024)              |     | /125.9Hz |                 | DA13 to $0 = H'0040$ to H'3FFF                             | 10       | 0 | 0     | 0     | 0     | 31.78        |

|   | 0          | 1 | 1   | 124.12                | 0   | 7.94     | 2.03            | Always low/high output                                     | 14       |   |       |       |       | 2033.60      |

|   |            |   |     |                       |     | (ms)     | (s)             | DA13 to $0 = H'0000$ to H'00FF<br>(Data value) $\cdot$ T   | 12       |   |       | 0     | 0     | 508.40       |

|   |            |   |     |                       |     | /125.9Hz |                 | DA13 to 0 = H'0100 to H'3FFF                               | 10       | 0 | 0     | 0     | 0     | 127.10       |

|   |            |   |     |                       | 1   | 31.78    | 2.03            | Always low/high output                                     | 14       |   |       |       |       | 2033.60      |

|   |            |   |     |                       |     | (ms)     | (s)             | DA13 to $0 = H'0000$ to $H'003F$<br>(Data value) $\cdot T$ | 12       |   |       | 0     | 0     | 508.40       |

|   |            |   |     | (φ/4096)              |     | /31.5Hz  |                 | DA13 to 0 = H'0040 to H'3FFF                               | 10       | 0 | 0     | 0     | 0     | 127.10       |

|   | 1          | 0 | 1   | 496.48                | 0   | 31.78    | 8.13            | Always low/high output                                     | 14       |   |       |       |       | 8134.41      |

|   |            |   |     |                       |     | (ms)     | (s)             | DA13 to $0 = H'0000$ to H'00FF<br>(Data value) $\cdot$ T   | 12       |   |       | 0     | 0     | 2033.60      |

|   |            |   |     |                       |     | /31.5Hz  |                 | DA13 to 0 = H'0100 to H'3FFF                               | 10       | 0 | 0     | 0     | 0     | 508.40       |

|   |            |   |     |                       | 1   | 127.10   | 8.13            | Always low/high output                                     | 14       |   |       |       |       | 8134.41      |

|   |            |   |     |                       |     | (ms)     | (s)             | DA13 to $0 =$ H'0000 to H'003F<br>(Data value) · T         | 12       |   |       | 0     | 0     | 2033.60      |

|   |            |   |     | (φ/16384)             |     | /7.9Hz   |                 | DA13 to $0 = H'0040$ to H'3FFF                             | 10       | 0 | 0     | 0     | 0     | 508.40       |

|   | 1          | 1 | 1   | Setting<br>prohibited |     |          |                 |                                                            |          |   |       |       |       |              |

Fixed DADR Bits

Note: \* Indicates the conversion cycle when specific DA3 to DA0 bits are fixed.

PCSR

Figure 10.3 Output Waveform (OS = 0, DADR corresponds to  $T_L$ )

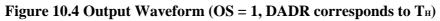

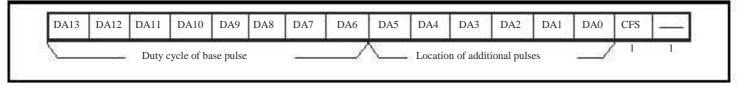

An example of the additional pulses when CFS = 1 (base cycle = resolution (T)  $\cdot$  256) and OS = 1 (inverted PWM output) is described below. When CFS = 1, the upper eight bits (DA13 to DA6) in DADR determine the duty cycle of the base pulse while the subsequent six bits (DA5 to DA0) determine the locations of the additional pulses as shown in figure 10.5.

Table 10.4 lists the locations of the additional pulses.

Figure 10.5 D/A Data Register Configuration when CFS = 1

In this example, DADR = H'0207 (B'0000 0010 0000 0111). The output waveform is shown in figure 10.6. Since CFS = 1 and the value of the upper eight bits is B'0000 0010, the high width of the base pulse duty cycle is  $2/256 \cdot (T)$ .

Since the value of the subsequent six bits is B'0000 01, an additional pulse is output only at the location of base pulse No. 63 according to table 10.4. Thus, an additional pulse of  $1/256 \cdot (T)$  is to be added to the base pulse.

Figure 10.6 Output Waveform when DADR = H'0207 (OS = 1)

However, when CFS = 0 (base cycle = resolution (T)  $\cdot$  64), the duty cycle of the base pulse is determined by the upper six bits and the locations of the additional pulses by the subsequent eight bits with a method similar to as above.

| 8<br>8        | 00                 | 00   | 00        | 0            | 00     | 0         | 00           | 20     | 0            | 00        | 0            | 00 |           | 00        | 0            | 00        | 0         | 00       | 00   | 00       | 0   |          |           |           |     |           |           |     |     |           |     |           | 00 | 00            |     | 00            | 00 |           |    |             |    |

|---------------|--------------------|------|-----------|--------------|--------|-----------|--------------|--------|--------------|-----------|--------------|----|-----------|-----------|--------------|-----------|-----------|----------|------|----------|-----|----------|-----------|-----------|-----|-----------|-----------|-----|-----|-----------|-----|-----------|----|---------------|-----|---------------|----|-----------|----|-------------|----|

| 61 6          |                    |      | +         | H            | $\pm$  | $\square$ | $\square$    | $\pm$  | $\square$    | $\pm$     |              | 00 | 0         | 00        | 0            | 0         | 0         | 00       | 0    | 00       | 0   |          |           |           |     |           |           |     |     |           |     |           | 00 | 00            | 00  | 0             | 00 | 00        | 00 | р¢          | 00 |

| 990           |                    |      |           | $\square$    | $\bot$ |           |              |        |              | -         |              |    |           |           |              | -         |           | -        |      |          |     |          |           |           |     |           |           |     |     |           |     | 00        | _  |               |     |               | _  |           | _  | 00          | _  |

| 33<br>53      | $\mathbb{H}$       | +    | +         | $\mathbb{H}$ | +      | 0         | 00           | 20     | 0            | 00        | 20           | oc | 20        | 00        | 0            | 00        | 20        | 00       | 20   | oc       | 0   | oc       | 000       | 200       | 00  | oc        | 0         |     |     |           |     |           |    |               | _   | _             | _  |           | _  |             | _  |

| 57 6          |                    |      | +         | H            | +      | Η         | H            | +      | $\square$    | +         | $\square$    |    | +         | +         | H            | +         | 0         | 00       | 0    | 00       | 0   | oc       | 00        |           | 00  | 00        | 0         |     |     |           |     |           |    |               |     |               |    |           |    |             |    |

| 56            |                    |      |           | $\Box$       | $\bot$ |           |              | $\bot$ | П            | $\bot$    | П            |    | $\square$ | $\bot$    | $\Box$       | $\bot$    |           |          |      |          |     |          |           |           |     |           |           |     |     |           |     |           |    |               |     |               | 0  | 00        | 00 | р¢          | 00 |

| 4 55          | $\square$          | +    | 0         | 0            | 00     | 0         | 00           | 20     | 0            | 00        | >0           | 00 | 20        | 00        | 0            | 00        | 0         | 00       | 20   | 00       | 0   | <u> </u> | 000       |           |     |           |           |     |     |           |     |           |    |               |     |               |    |           |    |             | -  |

| 9<br>8        | $\mathbb{H}$       | +    | +         | $\mathbb{H}$ | +      | Η         | $\mathbb{H}$ | +      | $\mathbb{H}$ | +         | $\mathbb{H}$ | +  | +         | 0         | 0            | 00        | 0         | 00       | 0    | 00       | 0   | oc       | 00        |           |     |           |           |     |     |           |     |           |    |               |     |               |    |           |    |             | 50 |

| 52            |                    |      |           |              |        |           |              |        |              |           | Π            |    | $\square$ |           |              |           |           |          |      |          |     |          |           |           |     |           |           |     |     |           |     |           |    |               |     |               |    |           |    | bс          |    |

| 50            |                    | _    | +         | $\square$    | +      | $\square$ | $\square$    | +      | 0            | 00        | 0            | 00 | 0         | 00        | 0            | 00        | 0         | 00       | 20   | 00       | 0   | oc       | 00        | 20        | 00  | 00        | 20        | oc  | 00  |           |     |           |    |               |     |               |    |           |    | 00          | -  |

| 6<br>6        | $\mathbb{H}$       | +    | +         | $\mathbb{H}$ | +      | Н         | $\mathbb{H}$ | +      | $\mathbb{H}$ | +         | $\mathbb{H}$ | +  | ++        | +         | H            | +         | +         | +        | +    | 00       | 20  | 00       |           |           | 00  | 00        | 0         | 00  | 000 |           |     |           |    |               |     |               |    |           |    |             |    |

| 48            |                    |      | $\top$    | H            | +      | H         | $\square$    | +      |              | +         | $\square$    |    | +         | +         | H            | +         |           |          |      |          |     |          |           |           |     |           |           |     |     |           |     |           |    |               |     |               |    |           |    | рc          | 00 |

| 4             |                    | 00   | 20        | 0            | 00     | 0         | 0            | ЭC     | 0            | 00        | 0            | 00 | 0         | 00        | 0            | 00        | 0         | 00       | 20   | oc       | 0   | oc       | +         |           | _   |           |           |     | 000 |           | _   |           | _  |               | _   |               | _  | + +       |    | 00          |    |

| 8             | $\mathbb{H}$       | +    | +         | $\mathbb{H}$ | +      | Н         | $\vdash$     | +      | $\mathbb{H}$ | +         | ++           | +  | Ы         | 00        |              |           |           | 0        | 5    | 00       |     |          |           | + +       | _   |           |           | _   |     |           |     |           |    |               |     | _             | _  |           | _  |             |    |

| 4             | $\mathbb{H}$       | +    | ╈         | $\mathbb{H}$ | +      | Η         | H            | +      | $\mathbb{H}$ | +         | $\mathbb{H}$ | +  | M         | Ť         | Ħ            | Ť         | Π         |          | Ť    |          | Ħ   | 1        | Ħ         | Ħ         | Ť   | ΜĒ        | M         |     | Ħ   | Ħ         |     | ΜĒ        | 0  | $\rightarrow$ | _   |               | _  | 0         |    | <u>ŏ</u> ċ  |    |

| <del>8</del>  |                    |      | $\Box$    | $\square$    |        |           | 0            | ЭC     | 0            | 00        | 0            | 00 | 0         | 00        | 0            | 00        | 0         | 00       | 0    | 00       | 0   | oc       | 00        | 0         | 00  | 00        | 0         |     | 00  | +++       | _   |           |    | 00            | 00  | 0             | 00 | 00        | 00 | рc          | 0  |

| 8             |                    |      | $\square$ | H            |        | $\square$ | $\square$    |        | +            | $\square$ |              |    | +         |           | ЦÍ           | $\square$ | $\square$ |          |      | 00       | Ц   |          |           |           |     |           |           |     |     |           |     |           |    |               |     |               |    | 00        |    |             |    |

| 8             | $\mathbb{H}$       | +    | +         | $\mathbb{H}$ | +      | H         | $\mathbb{H}$ | +      | +            | +         | +            | +  | +         | +         | $\mathbb{H}$ | +         | +         |          | 7    | 00       | 11  |          | M         | 11        | +   |           | Μ         |     | Ħ   | Ħ         |     |           | ٣  |               | 10  | Н             | 10 |           | 50 | 00          | 놂  |

| 39            |                    |      |           |              | 00     | 0         | 0            | oc     | 0            | 00        | 0            | 00 | 0         | 00        | 0            | 00        | 0         | 00       | 0    | 00       | 0   | oc       | 00        |           | 00  | 00        | 0         | oc  | 00  |           | 00  | 00        | 0  | 00            | 0   | 0             | 00 | 00        |    |             | 20 |

| 38            |                    |      |           | П            |        |           |              |        | П            |           | П            |    | Π         |           | Π            |           |           |          |      |          |     |          |           |           |     |           | _         |     | 00  | _         | _   | _         |    | _             | _   | -             |    | 00        |    |             | 20 |

| 6 37          | $\mathbb{H}$       | +    | +         | $\mathbb{H}$ | +      | H         | $\parallel$  | +      | $\parallel$  | +         | $\parallel$  | +  | +         | +         | H            | 00        | 20        | 00       | 0    | 00       | 0   | oc       | 000       | 00        | 00  | 00        | 20        | oc  | 00  | 200       | 00  | 00        | 20 | 00            | 0   |               | _  |           | _  |             |    |

| 35 3          | $\mathbb{H}$       | +    | +         | $\mathbb{H}$ | +      | Η         | H            | +      | $\mathbb{H}$ | 0         | bo           | 00 | 0         | 00        | 0            | 00        | 0         | 00       | 0    | 00       | 0   | oc       | 00        |           | 00  | 00        | 0         | oc  |     | 200       | 00  | 00        | 0  | 00            | 00  |               | _  | +         |    | <u>oc</u>   |    |

| 34            |                    |      |           | Ħ            | t      |           |              | T      | $\square$    | $\pm$     | Π            |    |           |           |              | 1         |           |          |      |          |     | T        | Ħ         |           |     |           |           |     |     |           |     | 00        |    |               |     |               |    |           | 00 | ЮĊ          | 00 |

| 8             | $\square$          | +    | +         | $\square$    | +      | $\square$ | $\vdash$     | +      | $\square$    | +         | $\square$    | +  | ++        | +         | $\square$    | +         | +         | +        | +    | +        | 0   | oc       | 000       | 200       | 00  | 00        | >0        | 00  | 00  | 200       | 00  | 00        | >0 | 00            | 00  | 00            | 00 | 00        | 0  | pp          | 20 |

| 8             |                    | 00   | 20        | 0            | 00     | 0         | 0            | 20     | 0            | 00        |              | 00 | 0         | 00        | 0            | 00        | 0         | 00       | 00   | 00       | 20  | 00       |           |           | 00  | 00        | 0         | 00  | 00  |           | 00  | 00        | 0  | 00            | 00  | 0             | 00 |           | 00 | bc          |    |

| 8             |                    |      |           |              |        | Ē         |              |        |              |           |              | _  |           |           |              |           |           |          |      |          |     |          | 00        |           | 00  | 00        | 20        | oc  | 00  | 00        | 00  | 00        | 0  | 00            | 00  | 0             | 00 | 0         | 00 | oc          | 00 |

| 8             |                    |      |           | $\square$    |        |           |              |        |              |           |              | C  | 0         | 00        | 0            | 00        | 0         | 00       | 0    | 00       | 0   | oc       | 00        |           | 00  | 00        | >0        | oc  | 00  | 200       | 00  | 00        | 20 |               |     | 00            | 00 | 00        |    | oc          | 20 |

| ñ<br>Li       | $\mathbb{H}$       | +    | +         | $\mathbb{H}$ | +      | Н         | 0            | 20     |              | 00        |              | 00 |           | 00        | 0            |           |           | 00       | 00   | 00       | 20  |          |           |           | 00  | 00        | 0         | 00  |     |           | 00  |           | 20 |               | 20  |               |    |           |    |             | 20 |

| 8             |                    |      | +         | H            | +      | H         | <u> </u>     | 1      |              |           |              |    | Ť         | 1         | Ĭ            | 1         |           |          | 1    |          |     |          | T         |           | -   |           | _         |     | 00  | _         | _   |           | _  | -             | _   | $\rightarrow$ | _  |           |    | ŏč          |    |

| ĸ             |                    |      |           | $\square$    |        |           |              |        |              | $\bot$    | П            |    |           |           | П            |           |           | 00       | 20   | 00       | 0   | oc       | 00        |           | 00  | 00        | 0         | oc  |     | 200       | 00  | 00        | 0  | 00            | 00  | 00            | 00 | 00        | 00 | oc          |    |

| 8             | $\mathbb{H}$       | +    | +         |              |        |           |              |        |              |           |              | 00 |           |           |              |           |           | 00       |      | 00       |     |          |           |           |     |           | 6         |     |     |           |     | H         | 0  |               |     |               |    | 20        | 20 |             |    |

| 8             | $\mathbb{H}$       | +    | +         | Ħ            | 1      | Η         | M            | 1      | M            | 7         | Ħ            |    | Ħ         | 7         | Ħ            | Ť         | Μ         |          | Ť    |          | M   | Ť        | Ħ         | Ħ         |     |           |           |     |     |           |     |           |    |               |     |               |    |           | 50 | <u> o</u> c |    |

| 2             |                    |      |           | Ħ            | T      |           |              | T      | $\square$    | $\pm$     | Π            |    | $\square$ | $\perp$   | 0            | 00        | 0         | 00       | 0    | 00       | 0   | oc       | 00        |           |     |           |           |     | 00  |           |     |           |    |               |     |               |    |           |    | рc          | 00 |

| 8             | $\square$          | +    | +         | $\square$    | +      | $\square$ | $\vdash$     | +      | $\square$    |           |              | ~  |           |           |              |           |           | ~        | -    | ~        |     |          |           |           |     |           |           |     |     |           |     |           | _  |               | 0   | 0             |    |           | 20 |             |    |

| 92<br>92      | $\mathbb{H}$       | +    | +         | $\mathbb{H}$ | +      | Н         | $\mathbb{H}$ | +      | $\mathbb{H}$ |           | 20           | oc | 10        | 00        | 9            | 90        | 0         | oc       | 0    | oc       |     |          | 100       |           | 00  | OC        | 10        | 00  | 100 |           | _   | 00        | _  |               | _   |               | _  |           |    |             |    |

| 4             |                    |      |           | Ħ            | t      |           |              | t      |              | $\pm$     |              |    | $\square$ | t         | Ħ            | $\pm$     |           |          |      | С        | 0   | oc       | 00        |           | 00  | 00        | 0         | oc  | 00  | 200       |     |           |    |               |     |               |    |           |    | рc          | 00 |

| 16            | Щ                  |      |           |              |        |           |              |        |              |           | L            | 00 |           | 0.0       |              |           |           | 0        |      | 000      |     |          |           |           | ~~~ |           | H         | 000 |     |           |     |           |    |               |     |               |    |           | -  |             |    |

| 14            | $\left  \right  $  |      | 19        | Р            | 10     | Р         |              | 10     | 19           | 90        | 19           | 00 | 19        | 90        | М            | 4         | 19        |          |      | 00       | 19  |          | 14        |           |     |           |           |     |     |           |     |           |    |               | 20  |               | 00 |           |    |             |    |

| 5<br>1        |                    |      |           | Ħ            |        | Ħ         |              |        | ╞            |           | ╞            |    |           | 00        | 0            | 00        | 0         | 00       | 0    | 00       | 0   | oc       | 000       |           | 00  | 00        | 0         | oc  |     | 00        | 00  | 00        | 0  | 00            | 00  | 0             | 00 | 0         | 20 | þ           | 00 |

| 5             | Щ                  |      |           | ЦŢ           | T      | П         | ЦĪ           |        |              |           |              |    |           |           |              |           |           |          |      |          |     |          |           |           |     |           |           |     |     |           | -   |           |    |               |     |               |    |           |    | 00          |    |

| -             | $\mathbb{H}$       | +    | +         | $\mathbb{H}$ | +      | H         | $\mathbb{H}$ | 0      | 0            | 00        | 20           | 00 | 20        | 00        | 0            | 00        | 20        | 00       | 00   | 00       | 0   | oc       | 00        | 201       | 00  | 00        | 20        | oc  |     |           |     |           |    |               |     |               |    |           |    |             |    |

| -<br>0        | H                  | +    | +         | H            | +      | H         | H            | +      | $^{++}$      | +         | $^{++}$      | +  | +         | +         | H            | +         | +         | +        | 0    | 00       | 0   | oc       | 000       |           | 00  | 00        | 0         | oc  |     | ++        | _   |           | _  | $\rightarrow$ | _   |               | _  | +         | _  | oc          | -  |

| 90            | Ш                  |      |           | Ħ            | 1      | Ħ         |              | 1      | □            |           | Ħ            |    | $\square$ |           | Ц            |           |           |          |      |          |     |          | $\square$ | $\square$ |     |           | $\square$ |     |     | $\square$ |     | $\square$ |    |               |     | $\square$     |    | $\square$ | 0  | oc          | 00 |

| 6 7           |                    |      | +         | H            | 0      | 0         | 0            | 20     | 0            | 00        | 0            | 00 | 0         | 00        | 0            | 00        | 0         | 00       | 20   | 00       | 0   | oc       | 00        | 0         | 00  | 00        | 20        | 00  |     | 20        | 00  | 00        | 20 | 00            | 20  | 0             |    | 00        | 20 |             | 10 |

| 9             | $\left  + \right $ | +    | +         | $\mathbb{H}$ | +      | H         | $\mathbb{H}$ | +      | $\mathbb{H}$ | +         | H            | +  | +         | +         | $\mathbb{H}$ | 0         | 0         | 00       | 0    | 00       | 0   | 00       | 00        |           | 00  |           |           |     |     |           |     |           |    |               |     |               |    |           |    |             |    |

| 4             |                    |      |           | ╘            |        | Ħ         |              |        |              |           |              |    |           |           |              |           |           |          |      |          |     |          |           | $\square$ |     | $\square$ | Π         |     |     |           |     | $\square$ |    |               |     |               | 00 | 0         | 00 | oс          | 0  |

| en            |                    |      |           | П            | T      | П         | $\square$    | T      | П            | T         | 0            | 00 | 0         | 00        | 0            | 00        | 0         | 00       | 0    | 00       | 0   | oc       | 00        |           | 00  | 00        | 0         | oc  | 00  | 200       | 00  | 00        | 0  | 00            | 00  | 00            | 00 | 00        | 00 | 00          | 20 |

| 1 2 3         | $\mathbb{H}$       | +    | +         | $\mathbb{H}$ | +      | H         | $\mathbb{H}$ | +      | $\mathbb{H}$ | +         | H            | +  | +         | +         | $\mathbb{H}$ | +         | +         | $\vdash$ | +    | +        | +   | 0        |           |           | -   |           | H         |     | 000 | 1         | 0   |           | 20 | 00            | 20  | 0             | 00 |           | 20 |             | 30 |

| 0             | $\mathbb{H}$       | +    | +         | H            | +      | Η         | H            | +      | H            | +         | H            | +  | +         | +         | H            | +         | +         | +        | +    | +        | Ħ   | 1        | Ħ         | Ħ         | 1   | H         | Ĥ         |     | Ħ   | Ħ         | 1   | ff        | Ĥ  |               | f   | Ħ             | Ť  | ff        | f  | ٢ŀ          | f  |

| •             |                    | en 4 | t un      | ω            | - 00   | 00        | e;           | - 12   | 9            | _         |              |    | 2         | 25        |              |           |           |          |      | 29<br>30 | 5   |          |           |           |     | 39        | 2         |     | 4   |           | 48  | 49<br>60  | 35 |               |     |               |    | 89        |    | 69          |    |

|               | -0                 | -    |           | +            | - 0    | -         |              | _      | ++           | <u>-</u>  | 0            |    |           |           | 0            | - 0       |           | <u></u>  | - lo |          |     | <u>-</u> | +++       | 0         | _   |           |           | 0-  | ++  |           | _   |           |    | $\rightarrow$ | - 0 |               |    |           | _  |             | 2- |

| 6 bits<br>0 0 | 00                 |      | , o<br>   |              |        |           |              | -  0   |              |           |              |    |           | <u></u> - | E            |           |           |          |      | 0 -<br>  |     | _        |           | +-+       | _   |           |           |     |     |           | - 0 |           | _  |               |     | e             |    |           |    |             | Ŧ  |

|               | 66                 |      |           | 0            | 구      | F         |              |        | -1-1         |           | +-+          | 00 |           | - 0       | 0            | • •       |           |          | · -  |          | + + | ••       | 00        | ,0        | - 0 | 0-        |           |     | ·   |           | - 0 | 00        | _  | 00            | 0   | 0             |    |           |    |             |    |

|               | 00                 | 00   | 0         | 06           | _      | <b>C1</b> | - T          |        | 0            | 00        | 1 1          |    | · – I     | _         | - T          | _         | 1         | - T-     | -    |          |     | 00       | 00        |           | - 0 | 00        | 9         | 00  |     |           |     |           | -  | - T           | 1   |               |    |           | _  | · •         |    |