### **SEMICON Solutions**

## IP Design Manual

Created: Duong Dang

Date: 10/03/09

#### Content

- Design Procedure

- Verification Plan Procedure

- Implementation Process

#### Content

- Design Procedure

- Verification Plan Procedure

- Implementation Process

#### **Design Procedure**

- Basic Policies

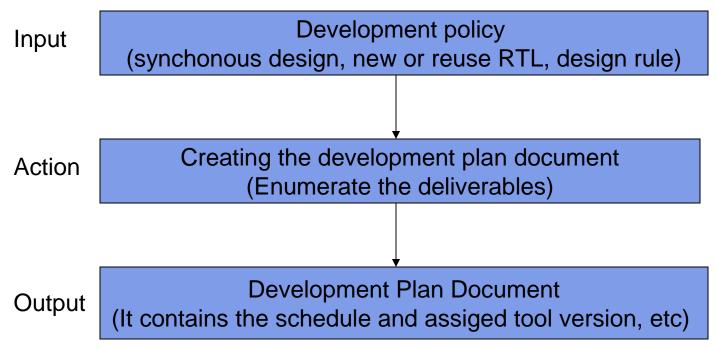

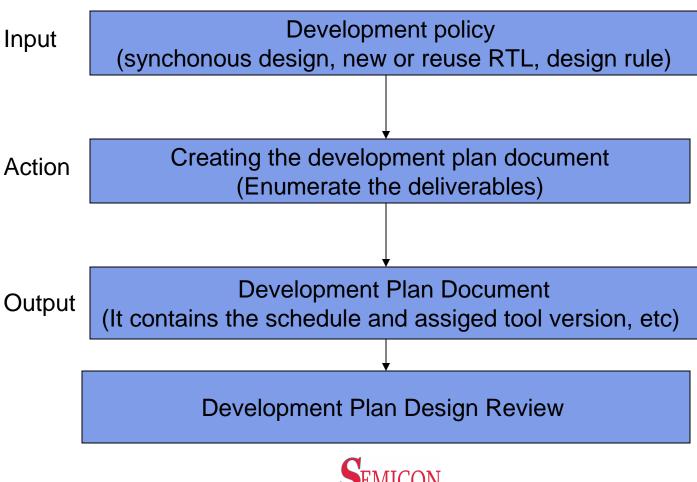

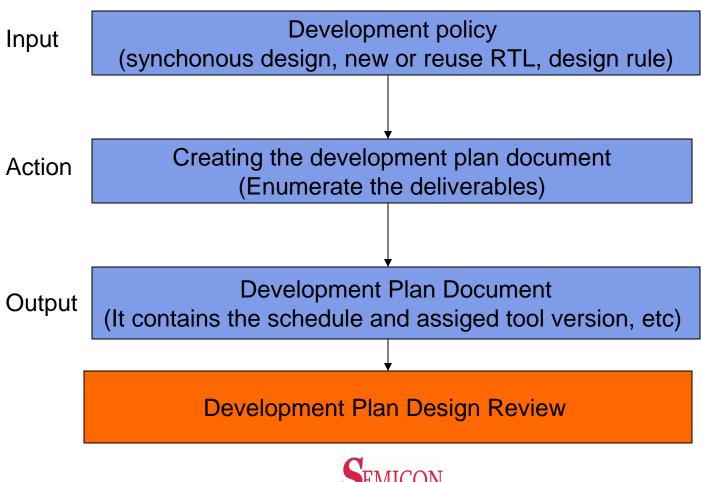

- Create the development plan

- Design function specification

- Design module detail

- The design procedure is recommende when IP is designed

- Design according to this procedure

- However, this procedure deviates according to the planning of development and requirement for design module.

- In this case, new procedure must be clear and output items and the quality equal with the procedure showed here

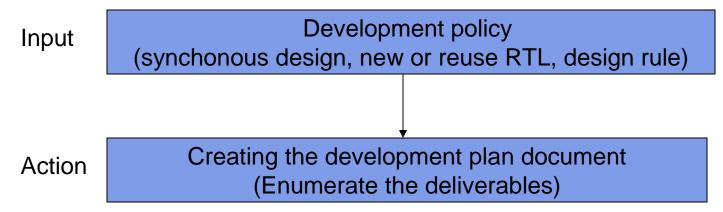

Input

Development policy (synchonous design, new or reuse RTL, design rule)

- Function specification design defines functions and operations of desiged module clearly

- Function spec must be neither lack or contradiction

- Description should be easy to understand

Input

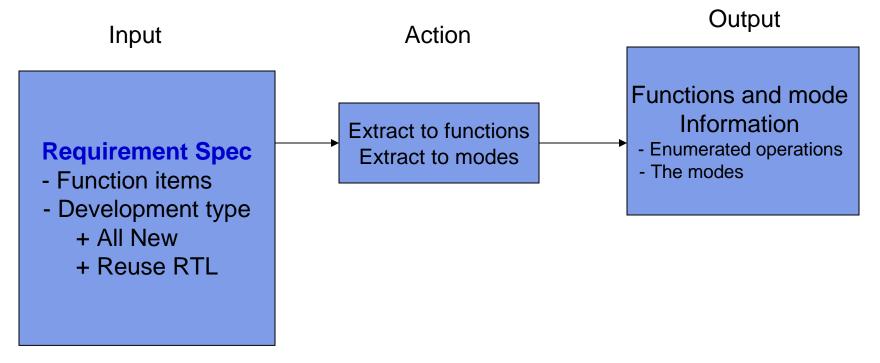

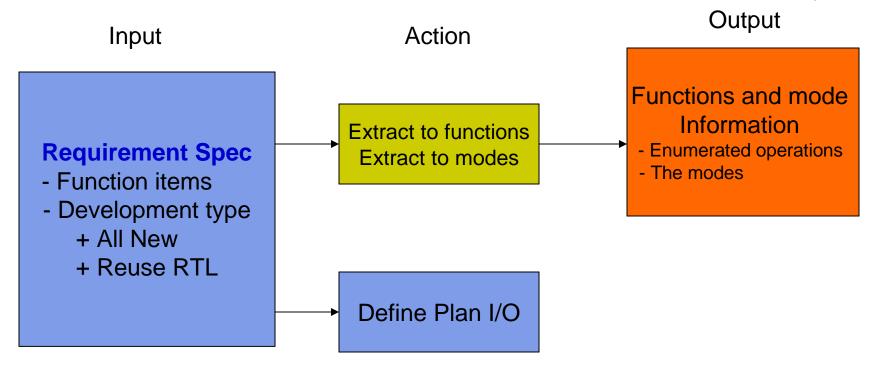

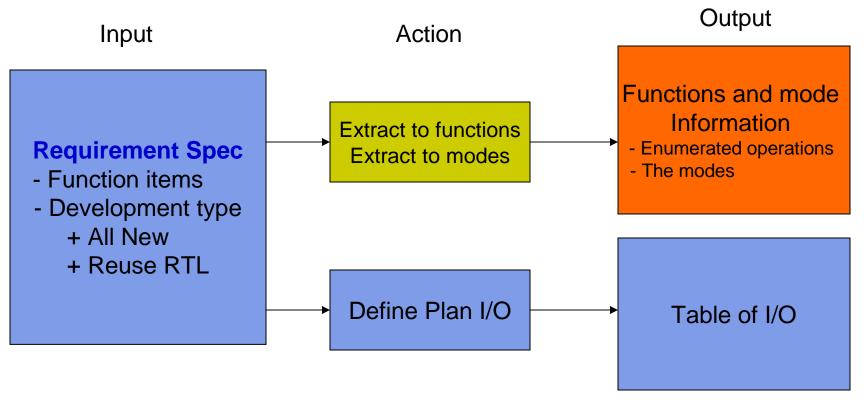

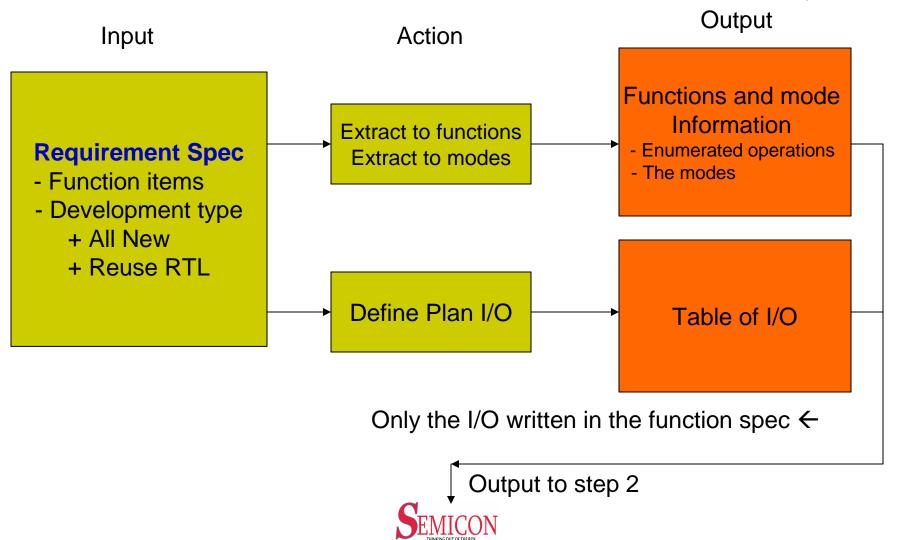

#### Requirement Spec

- Function items

- Development type

- + All New

- + Reuse RTL

Requirement Spec

- Function items

- Development type

+ All New

+ Reuse RTL

Action

Extract to functions

Extract to modes

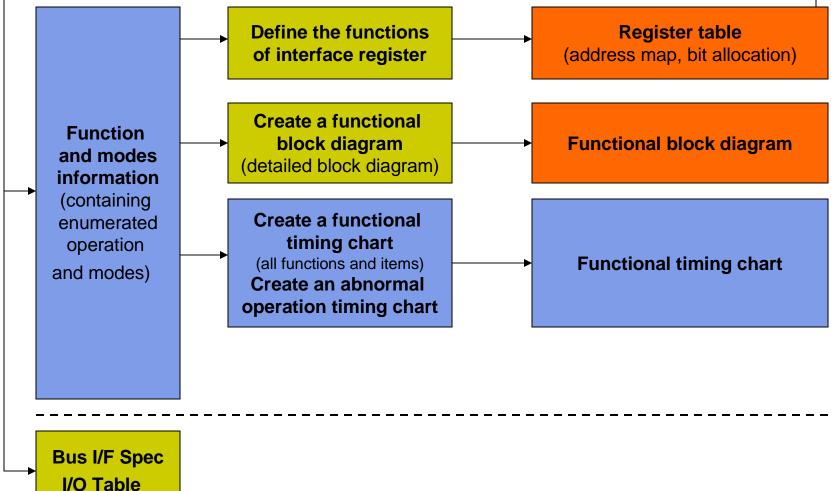

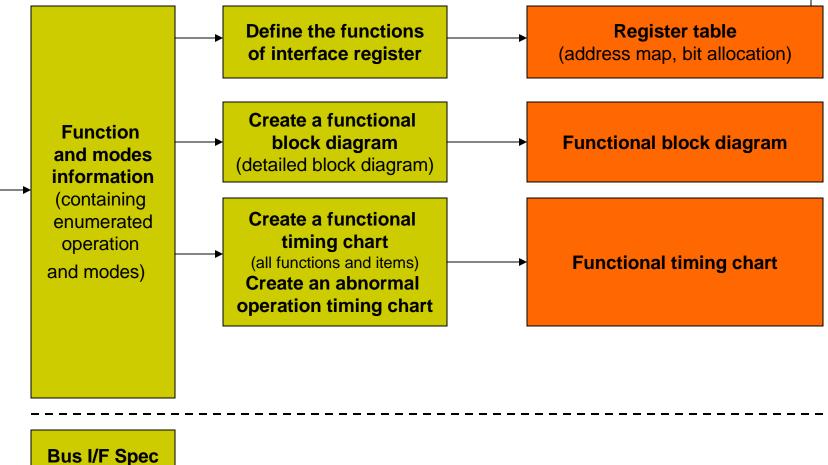

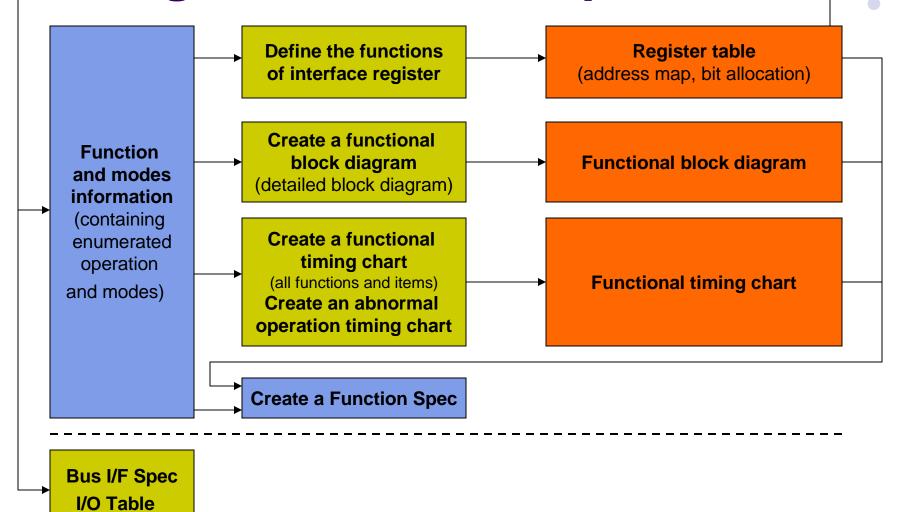

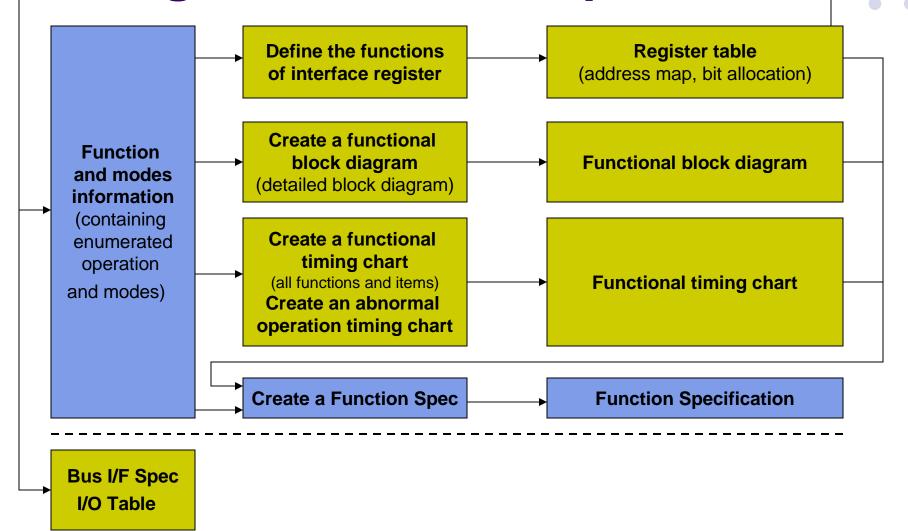

Function and modes information (containing enumerated operation and modes)

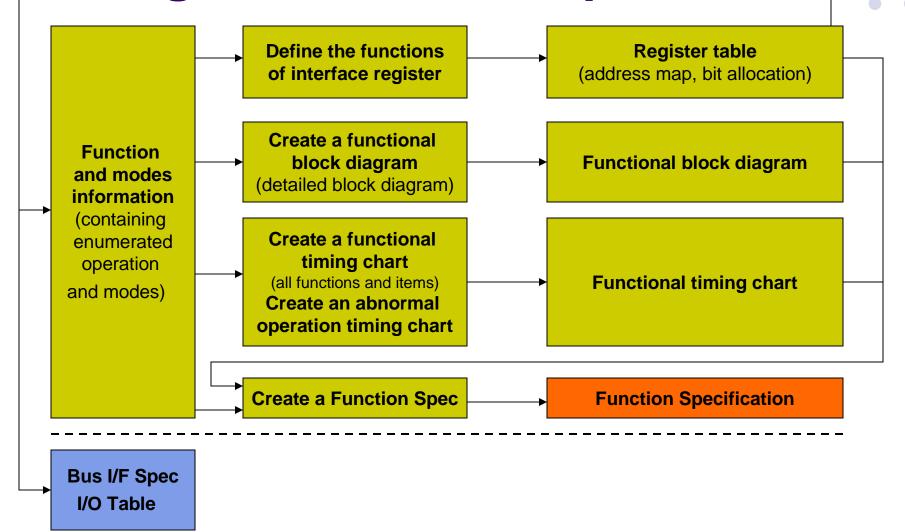

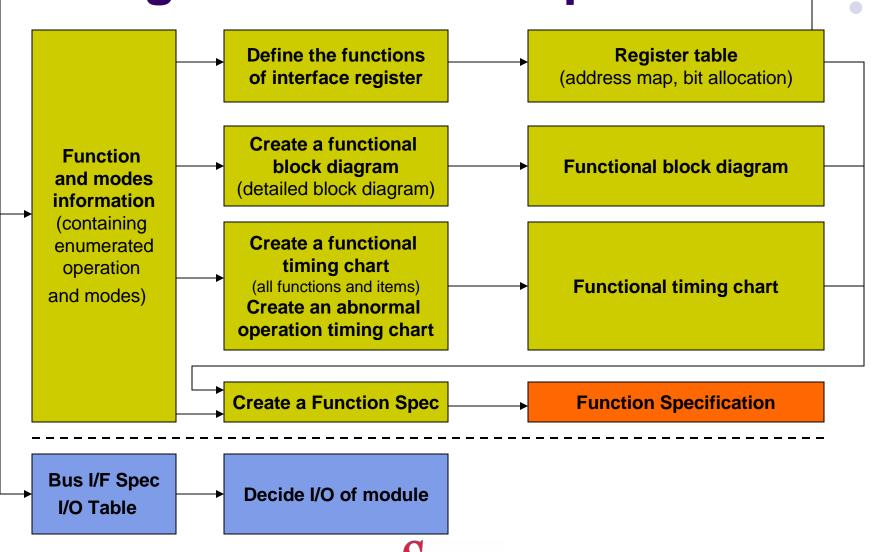

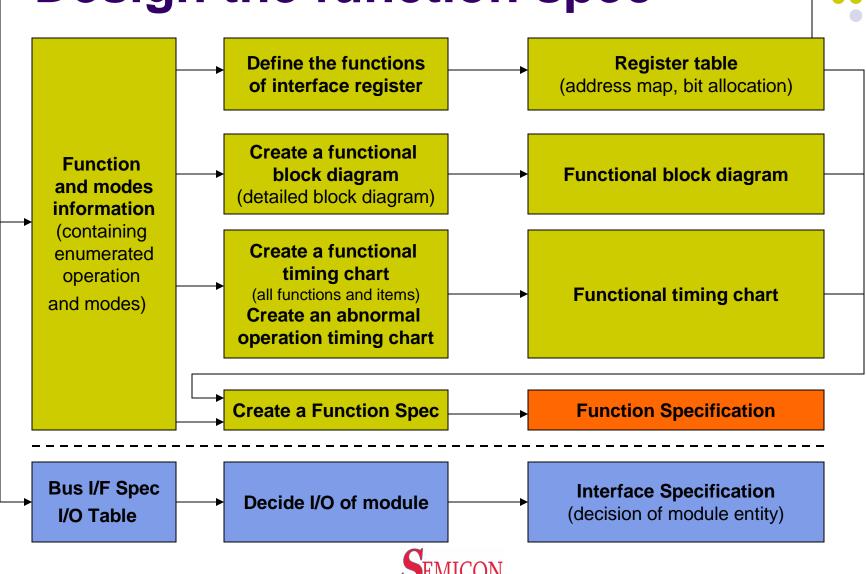

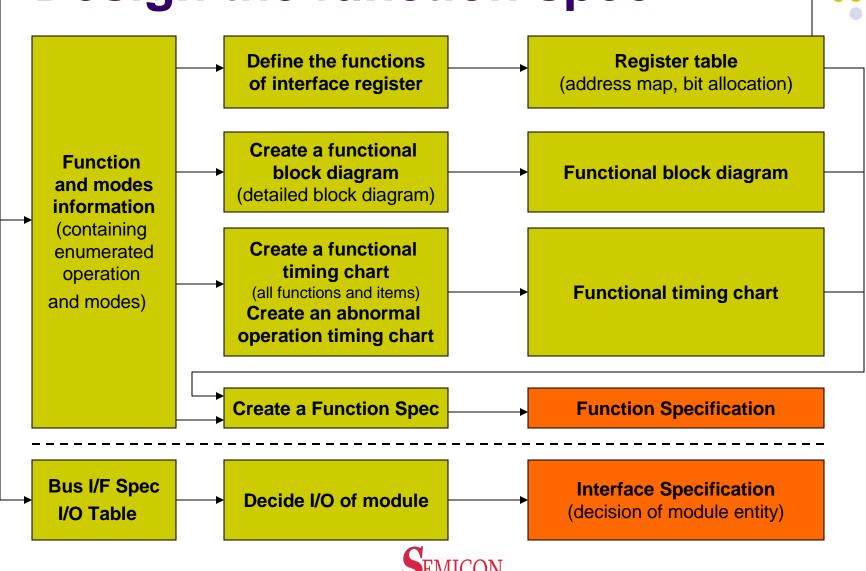

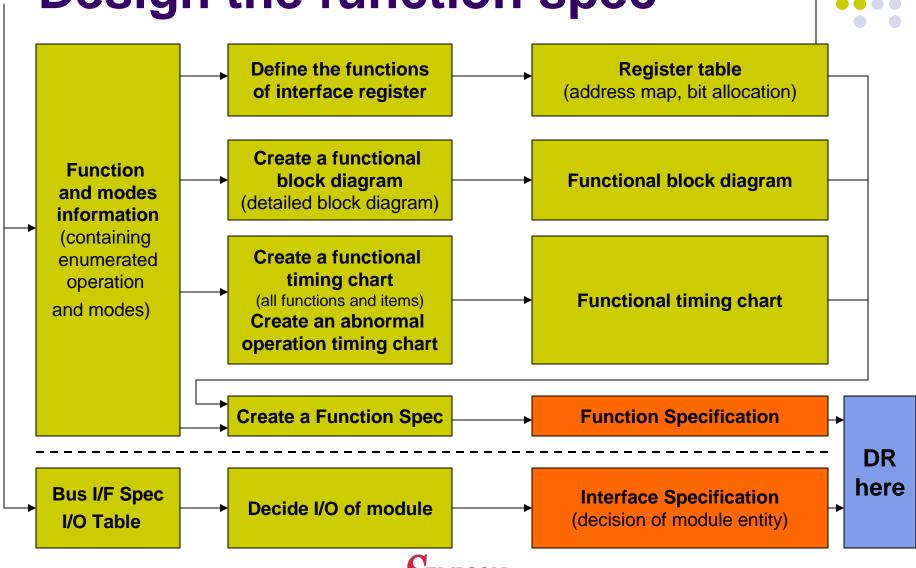

Define the functions of interface register

Function and modes information (containing enumerated operation and modes)

Define the functions of interface register

Register table (address map, bit allocation)

Function and modes information (containing enumerated operation and modes)

Define the functions of interface register

Register table (address map, bit allocation)

Function and modes information (containing enumerated operation and modes) Create a functional block diagram (detailed block diagram)

Function and modes information (containing enumerated operation and modes) Define the functions of interface register

Register table (address map, bit allocation)

Create a functional block diagram (detailed block diagram)

**Functional block diagram**

**Define the functions** Register table of interface register (address map, bit allocation) **Create a functional Function** block diagram **Functional block diagram** and modes (detailed block diagram) information (containing **Create a functional** enumerated timing chart operation (all functions and items) and modes) Create an abnormal operation timing chart

I/O Table

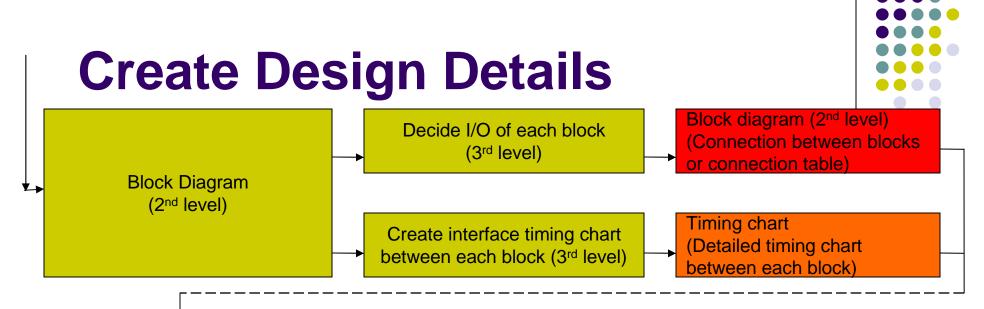

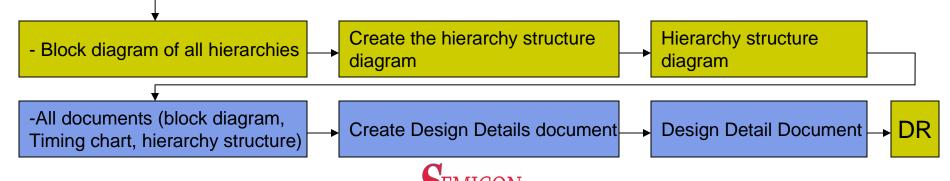

- The module is designed detail in this process

- A detailed design is a process of deciding how to realize the function and the operation that became clearly in the process of the function specification design

- Show how to realize the function by using the block diagram and the timing chart

- Clarifying that there are neither contradiction nor considered shortage of logic

- Descryption should be easy to understand

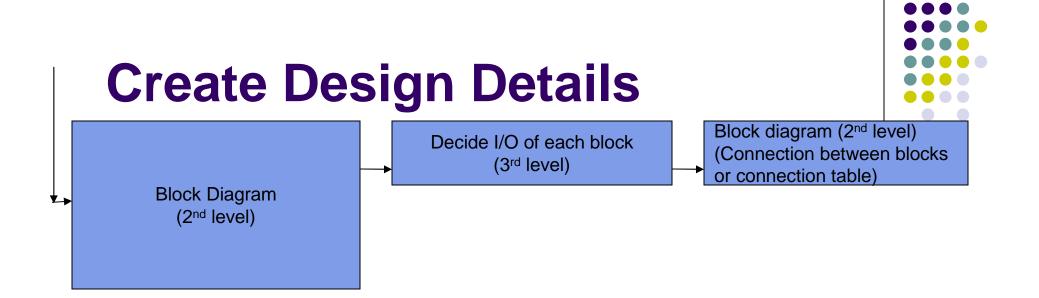

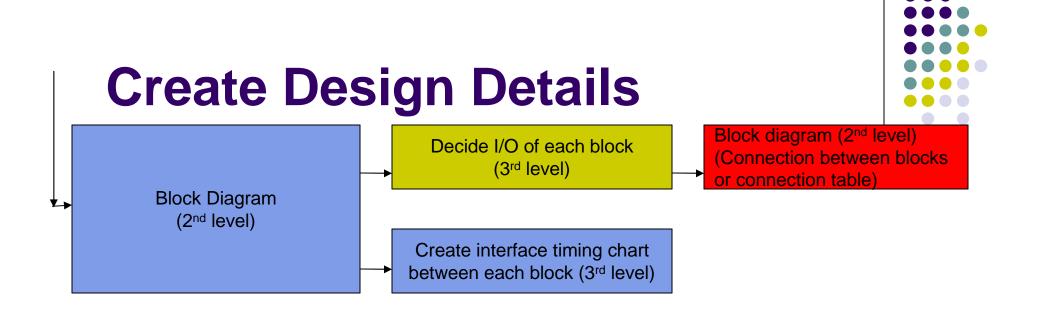

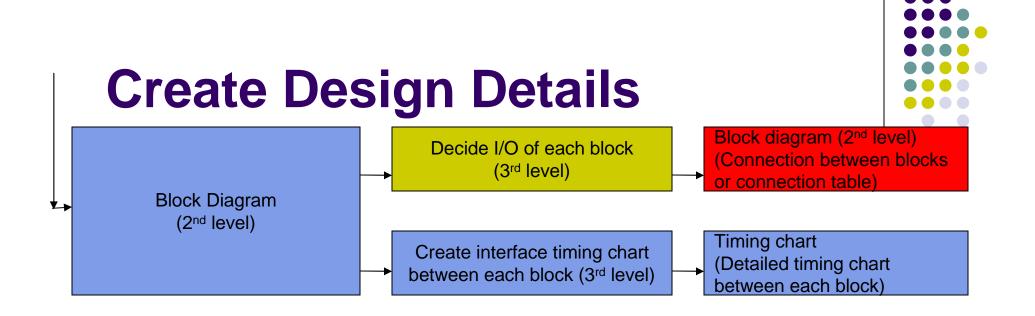

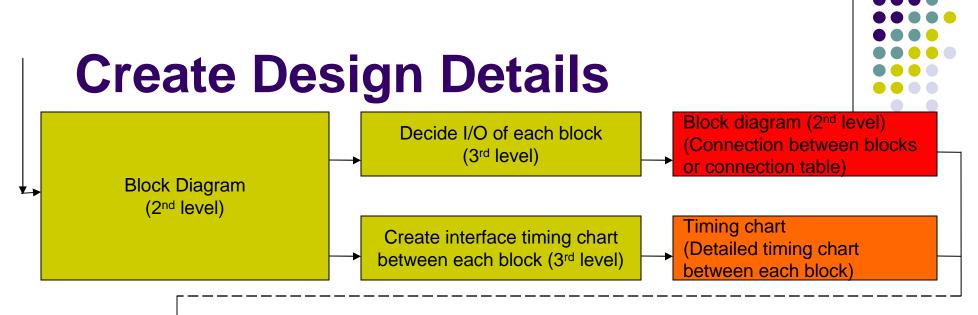

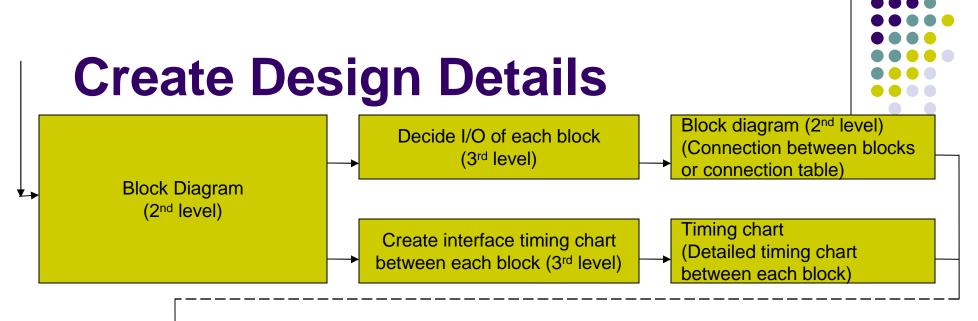

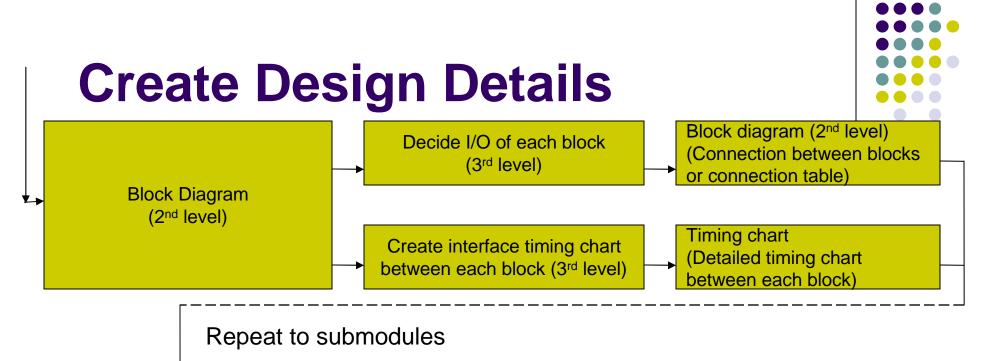

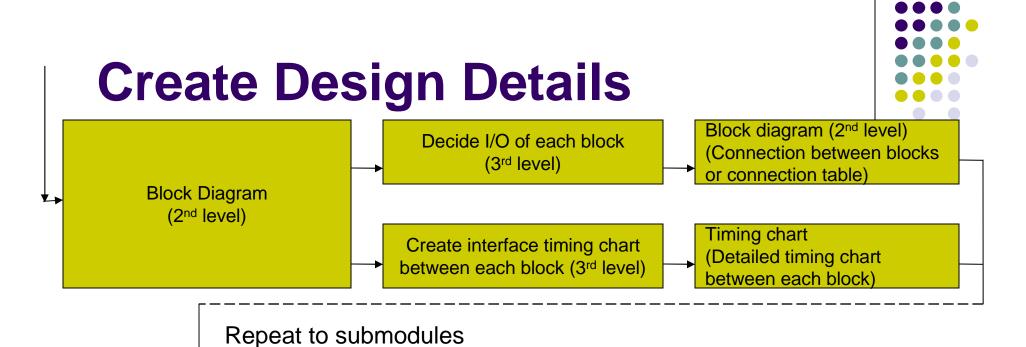

### **Create Design Details**

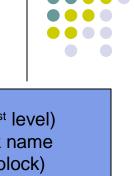

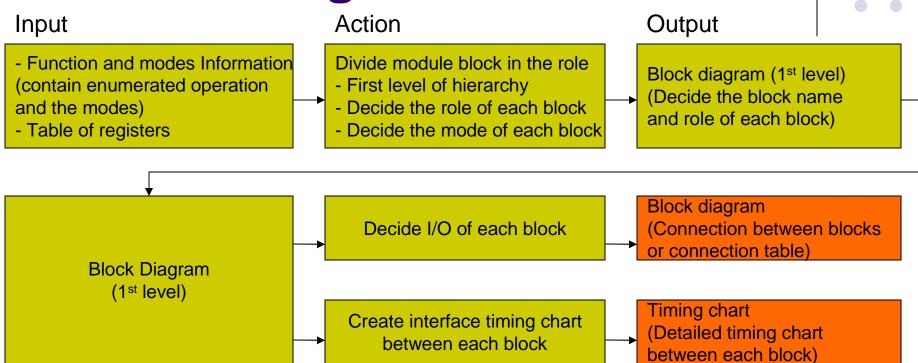

#### Input

- Function and modes Information (contain enumerated operation and the modes)

- Table of registers

### **Create Design Details**

Input Action

- Function and modes Information (contain enumerated operation and the modes)

- Table of registers

Divide module block in the role

- First level of hierarchy

- Decide the role of each block

- Decide the mode of each block

### **Create Design Details**

# Input

- Function and modes Information (contain enumerated operation and the modes)

- Table of registers

#### Action

Divide module block in the role

- First level of hierarchy

- Decide the role of each block

- Decide the mode of each block

#### Output

Block diagram (1st level) (Decide the block name and role of each block)

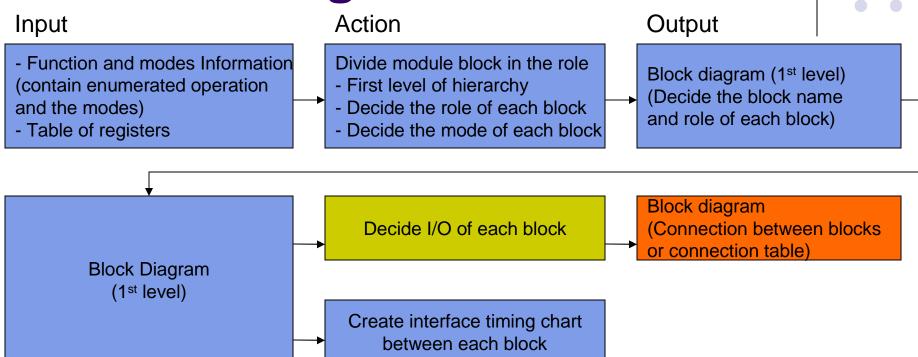

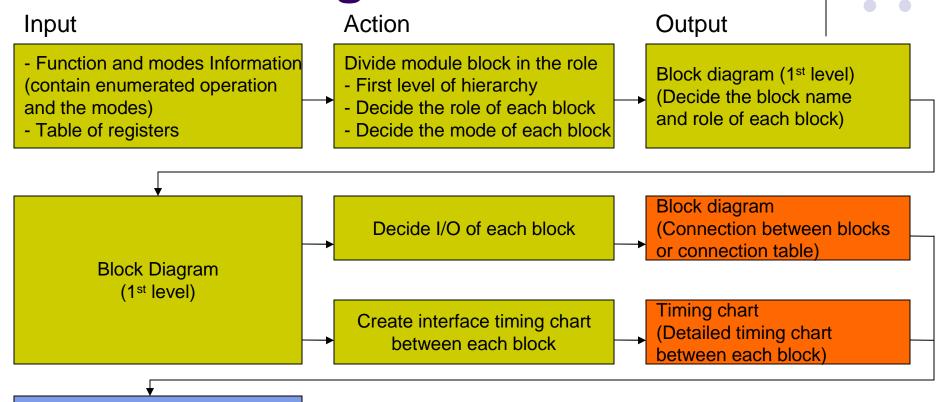

Input Action

- Function and modes Information (contain enumerated operation and the modes)

- Table of registers

Divide module block in the role

- First level of hierarchy

- Decide the role of each block

- Decide the mode of each block

Output

Block diagram (1st level) (Decide the block name and role of each block)

**Block Diagram** (1st level)

InputFunction and modes Information (contain enumerated operation

- Table of registers

and the modes)

Action

Divide module block in the role

- First level of hierarchy

- Decide the role of each block

- Decide the mode of each block

Output

Block diagram (1st level) (Decide the block name and role of each block)

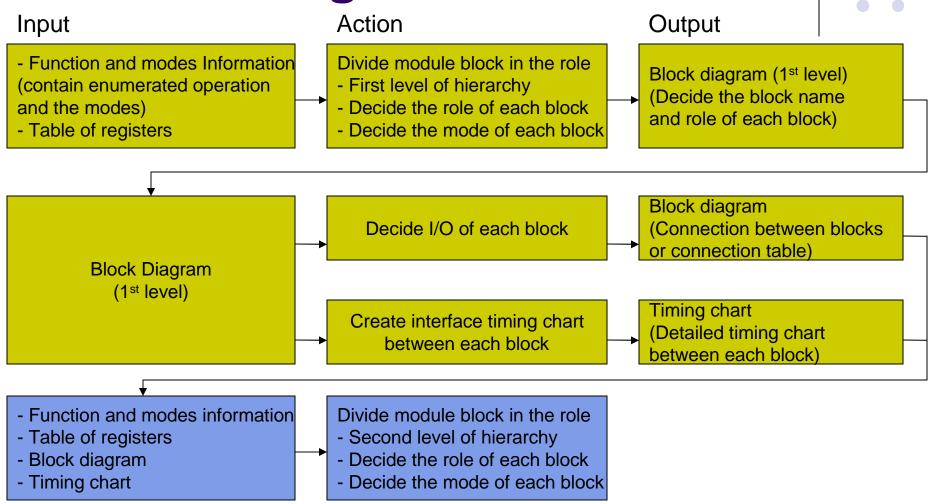

Block Diagram (1<sup>st</sup> level) Decide I/O of each block

- Function and modes information

- Table of registers

- Block diagram

- Timing chart

Next step

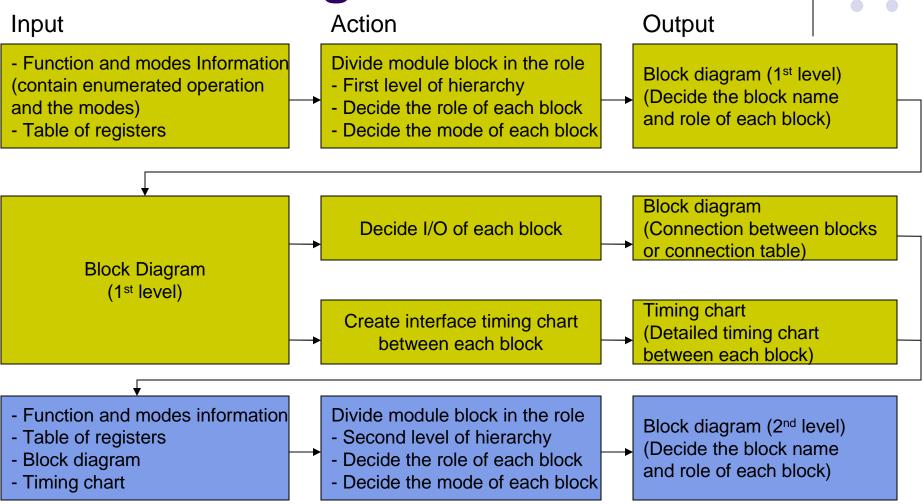

#### Action Input Output - Function and modes Information Divide module block in the role Block diagram (1st level) (contain enumerated operation - First level of hierarchy (Decide the block name and the modes) - Decide the role of each block and role of each block) - Table of registers - Decide the mode of each block Block diagram (Connection between blocks Decide I/O of each block or connection table) **Block Diagram** (1st level) Timing chart Create interface timing chart (Detailed timing chart between each block between each block) - Function and modes information Divide module block in the role Block diagram (2<sup>nd</sup> level) - Second level of hierarchy - Table of registers (Decide the block name - Block diagram - Decide the role of each block and role of each block) - Timing chart - Decide the mode of each block

Block Diagram (2<sup>nd</sup> level)

# Create Design Details Decide I/O of each block (3rd level) Block Diagram (2nd level)

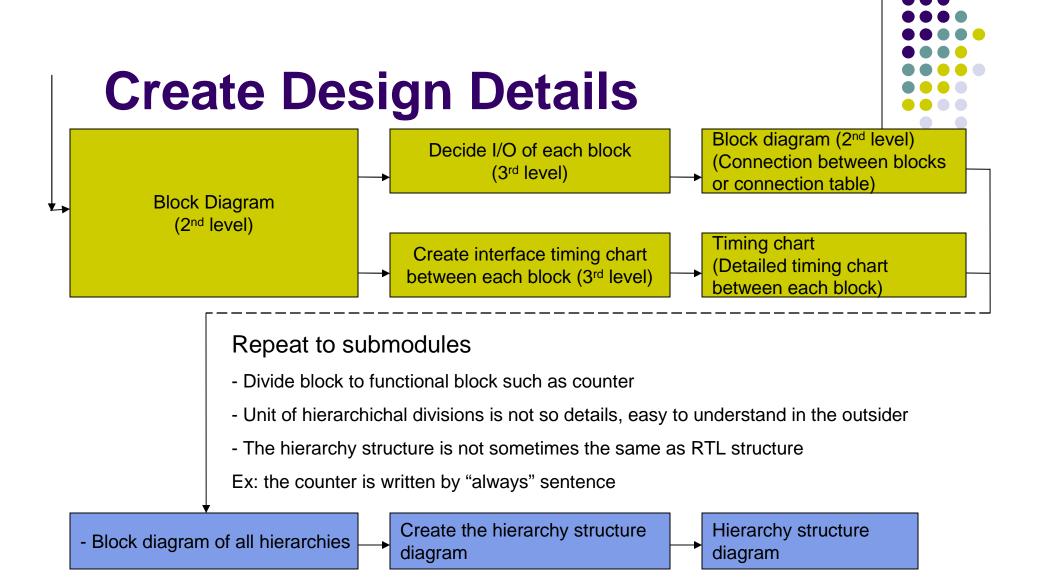

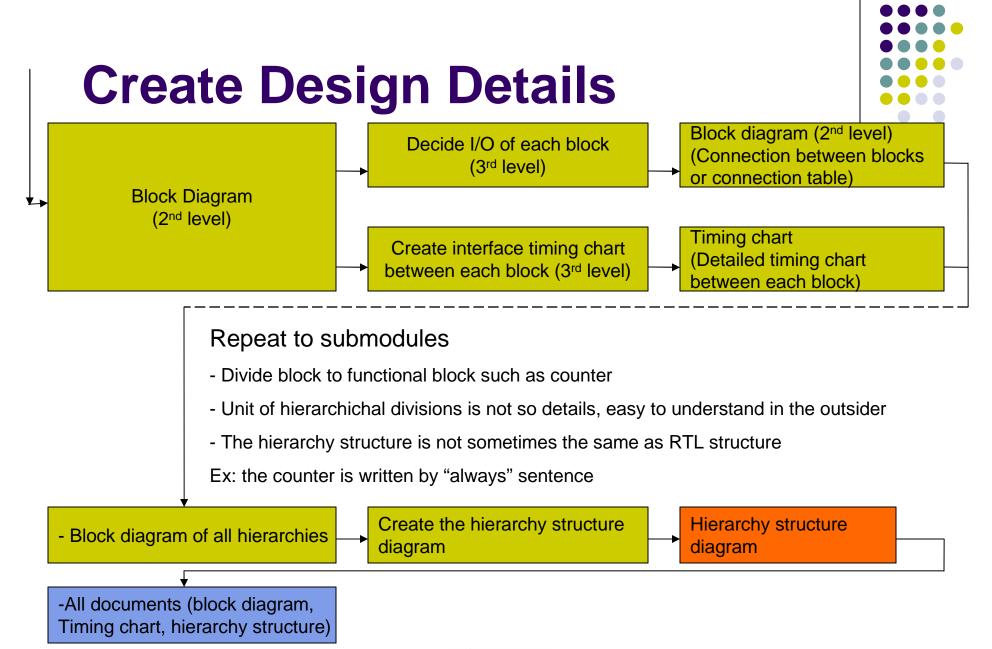

#### Repeat to submodules

- Divide block to functional block such as counter

- Unit of hierarchichal divisions is not so details, easy to understand in the outsider

- The hierarchy structure is not sometimes the same as RTL structure

Ex: the counter is written by "always" sentence

#### Repeat to submodules

- Divide block to functional block such as counter

- Unit of hierarchichal divisions is not so details, easy to understand in the outsider

- The hierarchy structure is not sometimes the same as RTL structure

Ex: the counter is written by "always" sentence

- Block diagram of all hierarchies

#### Repeat to submodules

- Divide block to functional block such as counter

- Unit of hierarchichal divisions is not so details, easy to understand in the outsider

- The hierarchy structure is not sometimes the same as RTL structure

Ex: the counter is written by "always" sentence

- Block diagram of all hierarchies diagram

- Divide block to functional block such as counter

- Unit of hierarchichal divisions is not so details, easy to understand in the outsider

- The hierarchy structure is not sometimes the same as RTL structure

Ex: the counter is written by "always" sentence

- Divide block to functional block such as counter

- Unit of hierarchichal divisions is not so details, easy to understand in the outsider

- The hierarchy structure is not sometimes the same as RTL structure

Ex: the counter is written by "always" sentence

## Content

- Design Procedure

- Verification Plan Procedure

- Implementation Process

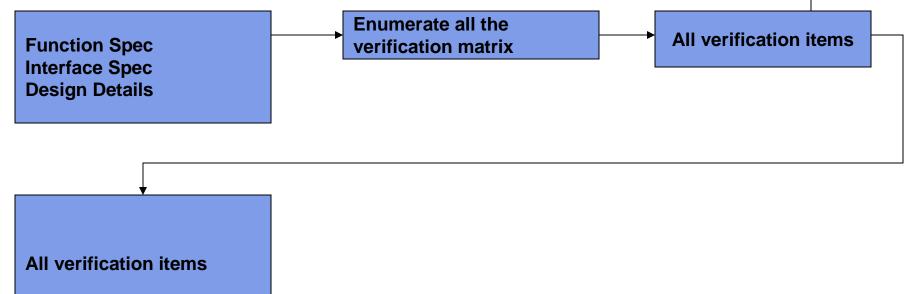

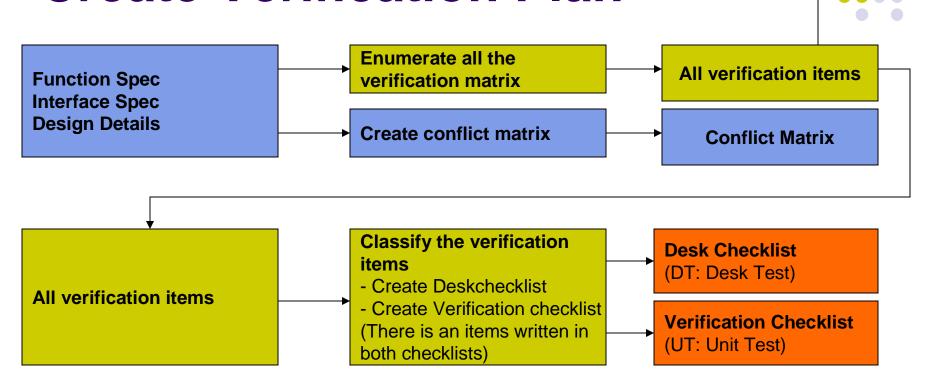

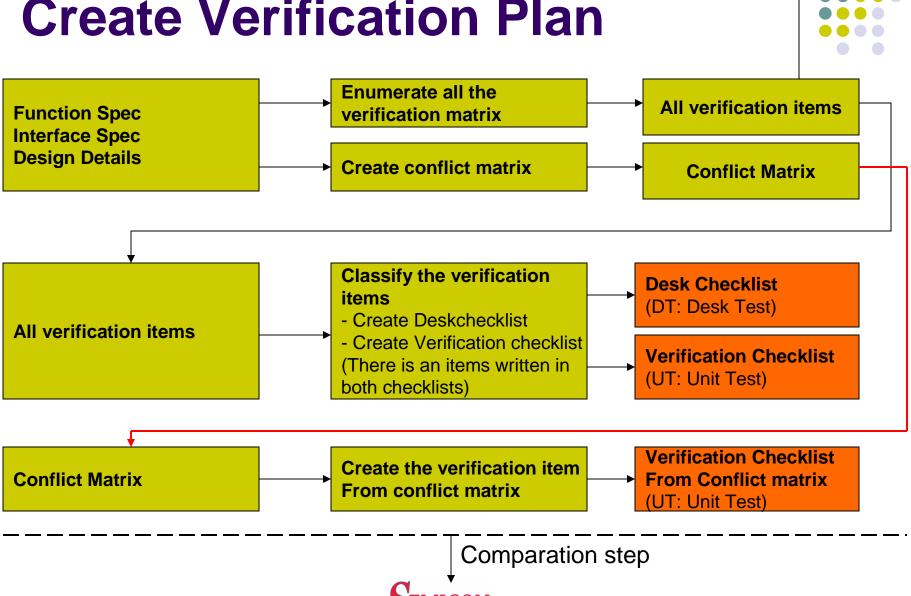

Function Spec Interface Spec Design Details

Function Spec Interface Spec Design Details **Enumerate all the verification matrix**

Function Spec Interface Spec Design Details **Enumerate all the verification matrix**

All verification items

- Whole image of verification plan is understood by planning the function verification plan

- Verification methodology and verification schedule can be estimated

- Enumerate all verification items to understand whole image of the function verification accurately

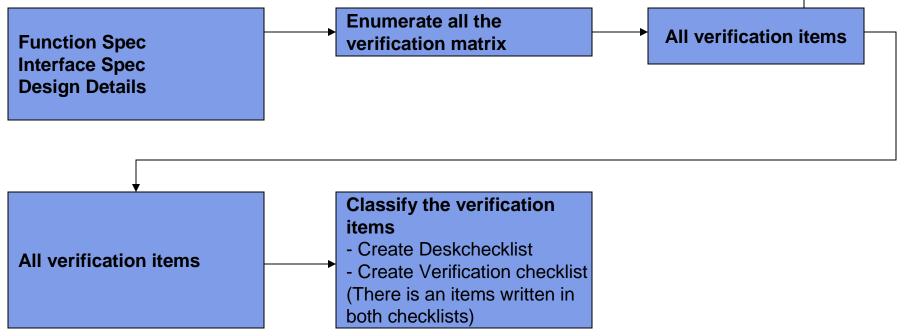

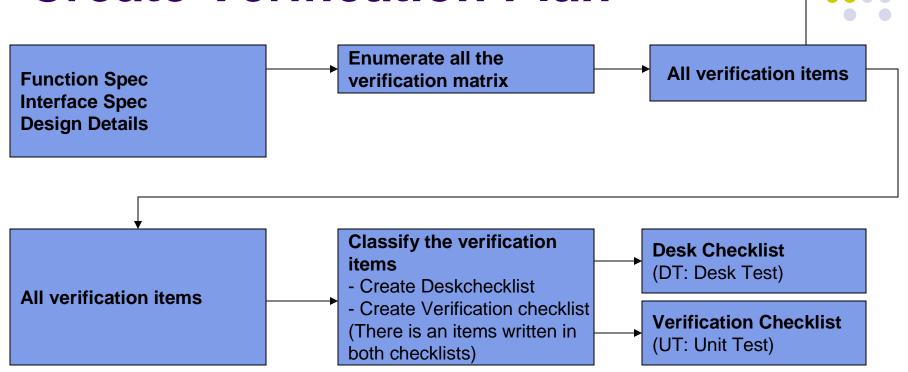

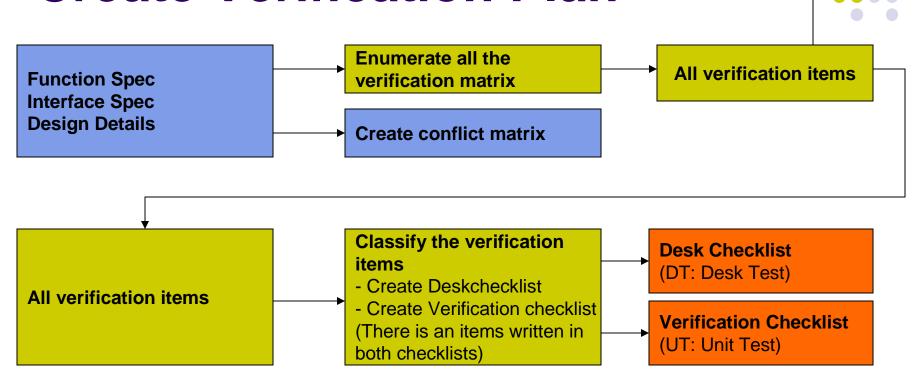

- Classify the verification items based on the structure, the function of mode, etc.

- Finally, Judge covering verification item by yourself

- However, should be easy to explain the criteria to the outsider

### **Create Verification Plan**

Function Spec Interface Spec Design Details

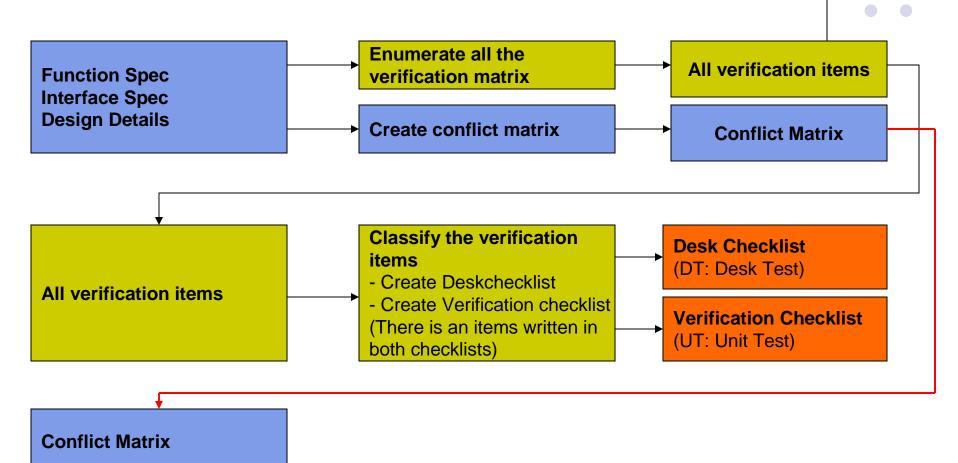

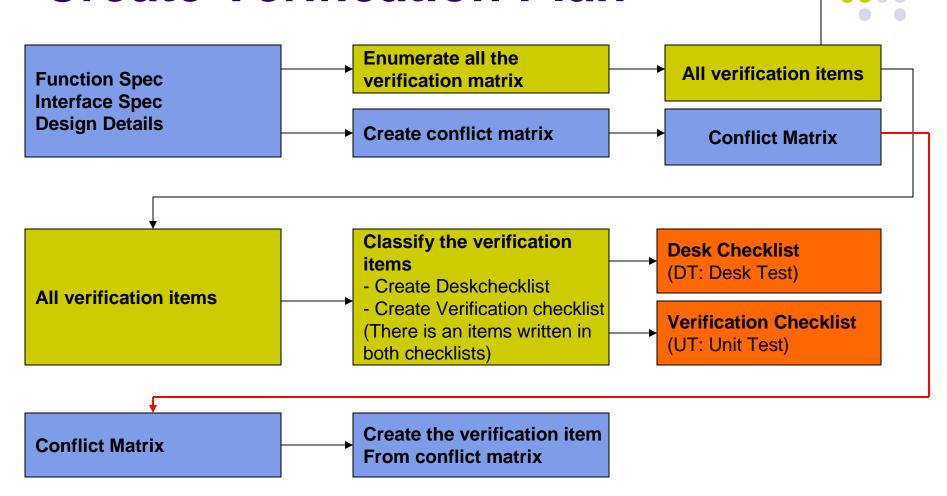

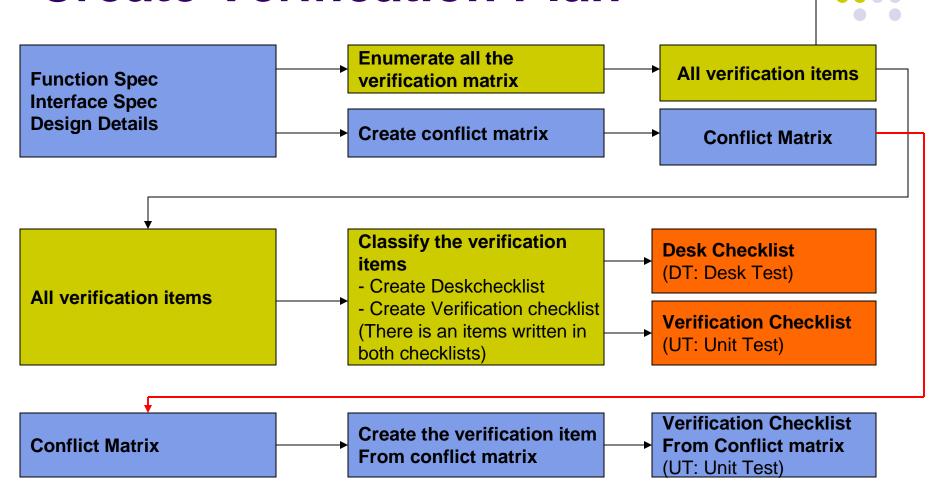

#### **Create Verification Plan**

Function Spec Interface Spec Design Details

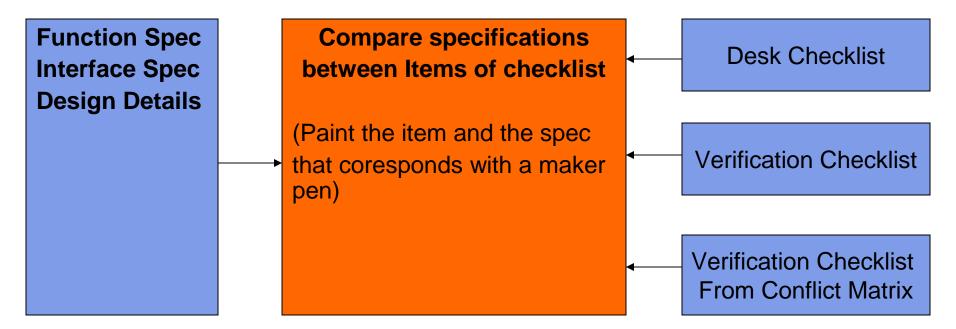

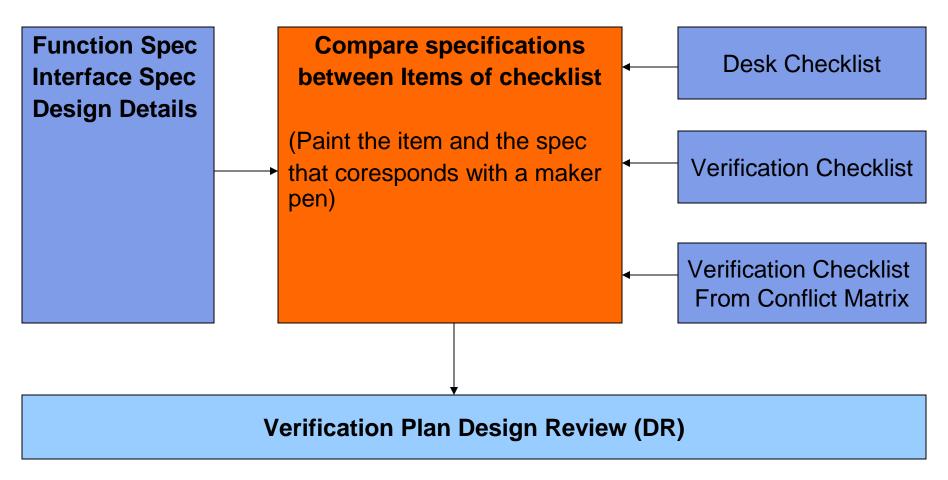

**Desk Checklist**

**Verification Checklist**

Verification Checklist From Conflict Matrix

#### **Create Verification Plan**

# View of enumerating verification items

- Normal function

- Extract the verification item from the function specification

- Extract the verification item from CPU interface register

- Extract the verification item from the modes

- Combination of normal function

- Extract the verification item that combines the above mentioned normal function

- Continous operation

- Continuous operation (R -> W -> R) or (R -> R -> R)

- White box verification item

- Verification item seen from operation boundary condition

- Verification item seen from conflict condition

- Verifcation item seen from abnormal operation

## View of Creating Conflict Matrix

- E xtract the states (ST)

- Combination of values set to control FF = State (Dynamic state)

- Operatinal mode (Static state)

- Extract the event (EV)

- Input signal and combination of input signals

- Assert event and negate event

- Transaction event such as writing by CPU

- Create the ST & EV matrix

- Create the EV & EV matrix

- Combination before and behind time of event A and event B

- Event A and event B occur same time

- There are important meanings in looking each cell and the explanation enough of a completed matrix

## View of Classifying Verification Item

- Items descibed to Desk Checklist

- Descibe all function specification

- Confirm whether all items described in the function specification are written in RTL code

- Combination of all the thinking fuctions must be confirmed by desk check (Some items are selected and verified by simulation)

- Difficult items must be confirmed by simulation

- Items descibed to Verification Checklist

- Items selected from all verification items (Narrow it to a specific condition because it becomes huge in all verification item)

- Selection method: The item(including explanation) written in the function spec is not enumerated without fail

- (When verification items become huge, the role of desk check should be reviewed)

- Describe forgetting neither the test mode nor the concealment function (It is item that is sure to be described in Design Details)

### Content

- Design Procedure

- Verification Plan Procedure

- Implementation Process

**RTL Coding**

**RTL Coding**

TMs Creating

**RTL Coding**

TMs Creating

Verification by simulation

**RTL Coding**

TMs Creating

Verification by simulation

**RTL Coverage**

**RTL Coding**

TMs Creating

Verification by simulation

**RTL Coverage**

Synthesis and formal verification

**RTL Coding**

TMs Creating

Verification by simulation

**RTL Coverage**

Synthesis and formal verification

**Checking of Netlist**

**RTL Coding**

TMs Creating

Verification by simulation

**RTL Coverage**

Synthesis and formal verification

**Checking of Netlist**

DFT

SEMICON THINKING OUT OF THE BOX.

- Understand "Why do you do?" clearly

- Do not misunderstand each work as the purpose

- Clarify the output of each work for the understanding of correct purpose

- Clarify the quality demanded by the output

- The output of each work should be a demanded quality

- Consult the project leader when the output is not demanded quality by some reasons

- Report the work result bt the report documents, described result explicity when the output is a demanded quality

- Report on reason anf the background when it is not a demand for quality

- The format of the report is according to it when there is united format

## **Q & A**