Đối tượng hoạt động tuần tự:

Là loại đối tượng hoạt động với tín hiệu clock. Hay còn gọi đó là các phần tử logic tuần tự. Loại này bao gồm những phần tử thường gặp như: FlipFlop, Memory, RAM, …. Hoạt động của các phần tử này phụ thuộc hoàn toàn vào tín hiệu clock.

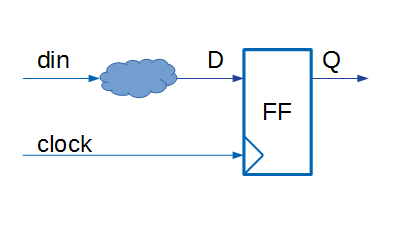

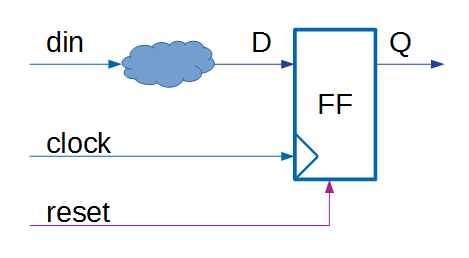

Ví dụ về phần tử tuần tự cơ bản nhất, đó là FlipFlop:

Các đặc trưng của FlipFlop:

1. Nguyên lý hoạt động:

Khi có 1 “trigger edge” tại đầu vào clock, giá trị đầu ra Q sẽ được gán bằng giá trị đầu vào D của FlipFlop.

2. Sườn kích hoạt ( trigger edge ):

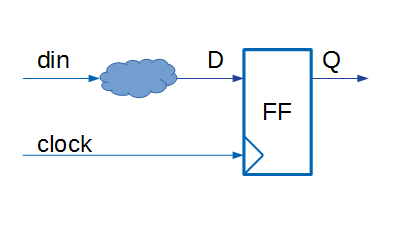

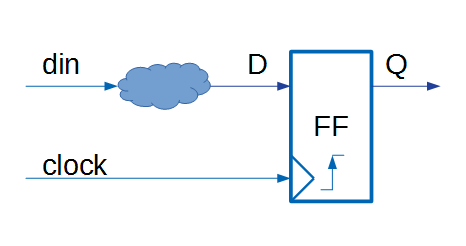

FlipFlop được kích hoạt bằng sườn của xung clock đầu vào. Tín hiệu clock thì lại có 2 sườn, sườn lên và sườn xuống. Do đó, nếu phân biệt FlipFlop bằng tín hiệu trigger thì có 2 loại, loại kích hoạt bằng sườn xuống và loại kích hoạt bằng sườn lên. ( Falling Edge Trigger and Rising Edge Trigger )

Rising Edge Trigger FlipFlop

Falling Edge Trigger FlipFlop

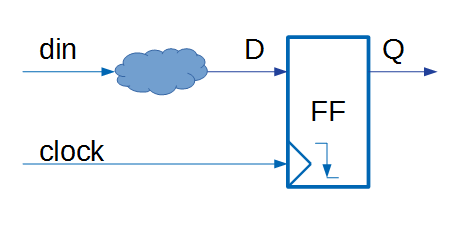

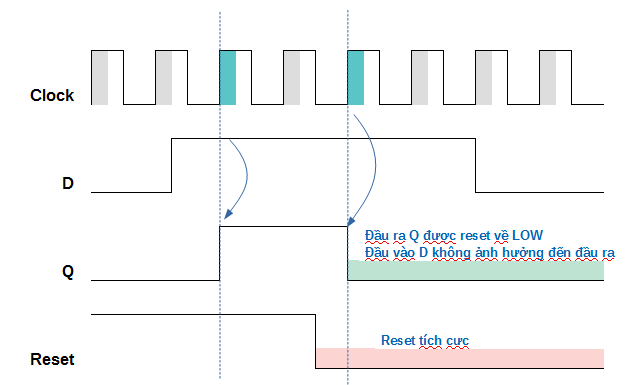

3. Hoạt động reset và tín hiệu reset:

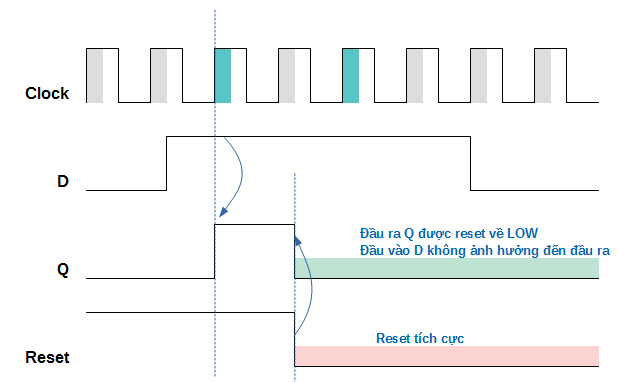

Hoạt động reset: FlipFlop có một hoạt động nữa liên quan đến giá trị đầu ra của nó, đó là hoạt động reset. Tín hiệu reset khi ở mức tích cực, sẽ có tác dụng đưa đầu ra Q của FlipFlop về một giá trị được xác định trước.

FlipFlop với tín hiệu Reset.

Mức tích cực của Reset: Tín hiệu reset tích cực theo mức Logic ( 0 hoặc 1 ), hoặc người ta có thể gọi là LOW hoặc HIGH. Do đó, có 2 khả năng tích cực của tín hiệu reset, đó là tích cực mức THẤP và tích cực mức CAO.

Đặc điểm đồng bộ với tín hiệu clock: Clock và Reset đều có thể là tín hiệu kích hoạt cho việc gán giá trị của tín hiệu đầu ra, do đó, trong thực tế, việc phân chia mức độ ưu tiên của 2 tín hiệu này sẽ dẫn đến 2 khái niệm, reset đồng bộ và reset bất đồng bộ.

+ Reset đồng bộ:

Đối với FlipFlop có reset đồng bộ, tín hiệu clock có ưu tiên cao hơn tín hiệu reset. Nó quyết định thời điểm sẽ kiểm tra mức tích cực của tín hiệu reset. Điều này có nghĩa là, tại mỗi thời điểm có sườn kích hoạt của clock, FlipFlop sẽ kiểm tra xem giá trị của tín hiệu reset tại thời điểm đó có bằng với mức tích cực hay không ? Nếu reset là tích cực, thì hoạt động reset sẽ xảy ra ngay lập tức. Ngược lại, hoạt động gán Q bằng D sẽ xảy ra. Nói cách khác, hoạt động reset phụ thuộc vào tín hiệu clock.

+ Reset bất đồng bộ:

Đối với FlipFlop có reset bất đồng bộ, tín hiệu clock và reset có mức ưu tiên là ngang nhau. Có nghĩa là, tại một thời điểm, nếu sườn kích hoạt của clock xảy ra, thì FlipFlop sẽ xảy ra hoạt động gán Q bằng đầu vào D; nếu bắt đầu mức tích cực thì hoạt động reset sẽ xảy ra. Nói cách khác, hoạt động reset chỉ phụ thuộc vào tín hiệu reset mà không phụ thuộc vào tín hiệu clock.

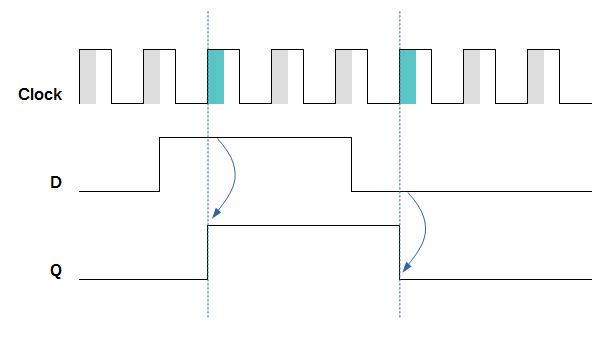

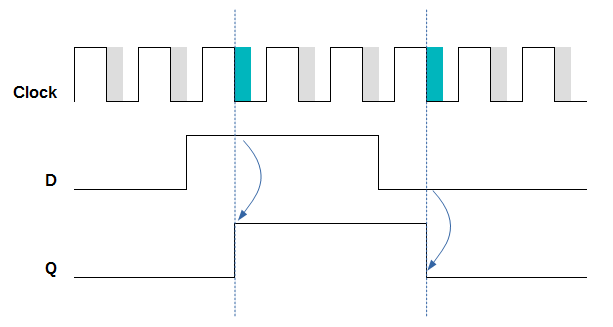

4. Dạng sóng của FlipFlop:

a. FlipFlop cơ bản. Không có tín hiệu Reset.

i, Tích cực sườn lên của clock:

ii, Tích cực sườn xuống của clock:

b. FlipFlop cơ bản. Có tín hiệu Reset.

i, Tích cực sườn lên của clock. Reset tích cực mức THẤP + Reset là đồng bộ:

ii, Tích cực sườn lên của clock. Reset tích cực mức THẤP + Reset là bất đồng bộ:

Các trường hợp còn lại của Waveform chúng ta chỉ cần đổi vị trí của sườn tích cực cho clock hoặc đổi mức tích của Reset là xong.

5. Các đặt tính khác của FlipFlop:

FlipFlop còn được gọi là Register ( bao gồm cả Latch ) ở một số phase của Chip design. Trong một số tool của Synopsy, Cadence... cũng có những lệnh, tên script dùng Register. Tên gọi register gắn liền với khái niệm của memory, bit nhớ, phần tử nhớ theo như chức năng của FlipFlop. Chứ năng nhớ ( memory ) của FlipFlop được thể hiện ở việc 1 giá trị đầu ra sẽ được điều khiển giữ nguyên hoặc cập nhật tùy theo logic của mạch được thiết kế. Hình dưới đây là 1 mạch điển hình thể hiện khả năng nhớ giá trị của FlipFlop:

Đối với dữ liệu, data, FlipFlop có thể được thiết dạng BUS gồm nhiều Bit đơn lẻ ghép lại. Ví dụ, DATA[31:0] là một bộ FlipFlop được tạo thành từ 32 FlipFlop đơn. Có một loại FlipFlop được thiết kế để tối ưu về power, area, đó là MultiBit FlipFlop. Loại này là MỘT FlipFlop có n bits. Do chỉ là 1 FlipFlop, nên nó chỉ cần 1 chân Clock đầu vào, các bit nhớ được thiết kế tối ưu hơn nhằm tiết kiệm diện tích của Cell.

Một đặc điểm vô cùng quan trọng của FlipFlop đó là về Timing. Đặc tính này quyết định đến tốc độ của thiết kế, và là tính chất quyết định đến thời gian phát triển dự án. Do tính chất quan trọng của Timing nên Admin sẽ có một Thread riêng về vấn đề này. Các bạn theo dõi sau nhé.

Nguồn: degic.freeforums

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn