HOW TO HANDLE INTERRUPT IN UVM?

Sunday, 10 July 2022 13:55

Semicon Editor 01

Interrupt handling is a well-known feature of any SoC which usually comprises of CPU, Bus Fabric, several Controllers, Sub-Systems & many IP blocks as part of it. In some way or other Interrupts are used to act as the sideband signals of the Design/IP Blocks & most of the time it’s not the part of the main bus or control bus. Interrupt handling is a well-known feature of any SoC which usually comprises of CPU, Bus Fabric, several Controllers, Sub-Systems & many IP blocks as part of it. In some way or other Interrupts are used to act as the sideband signals of the Design/IP Blocks & most of the time it’s not the part of the main bus or control bus.

Last Updated ( Monday, 03 April 2023 23:19 )

Read more...

|

Formal verification: where to use it and why?

Sunday, 10 July 2022 13:52

Semicon Editor 01

With innovations in technologies and methodology, the benefits of formal functional verification apply in many more areas. If we understand the characteristics of areas with high formal applicability, we can identify not only which blocks are good candidates, but also what portions or functionalities of the blocks will give the greatest return on the time and effort invested. Today, formal verification can be more valuable applied partially within blocks by choosing the functions that have the highest return.

Last Updated ( Sunday, 10 July 2022 13:55 )

Read more...

KEY AREAS TO CONSIDER DURING SOC VERIFICATION

Sunday, 10 July 2022 13:48

Semicon Editor 01

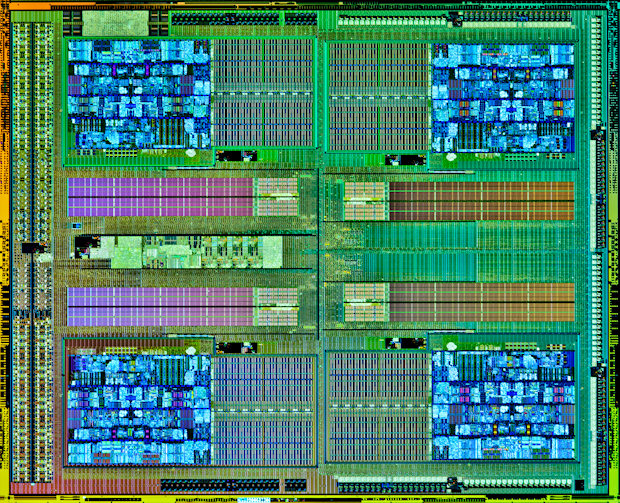

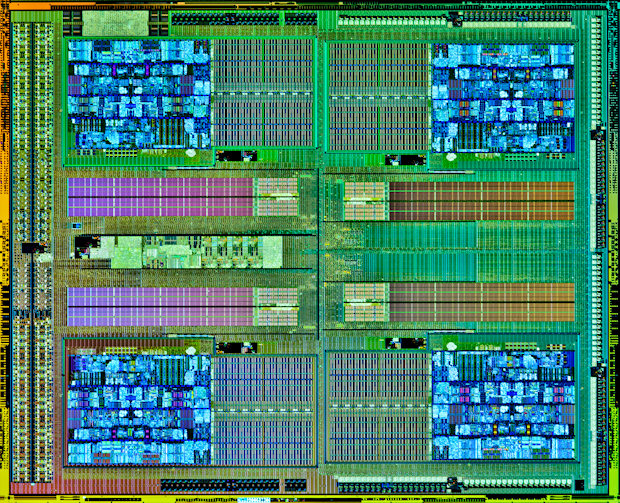

Over the years, design complexity and size have stubbornly obeyed the growth curve predicted by Intel co-founder Gordon Moore. Moore stated that the number of transistors on integrated circuits doubles approximately every two years. The chip makers want to pack as many functions as possible in their SoCs and provide as many feature additions to gain market share. The additional features increase the complexity and effort for verification.

Last Updated ( Sunday, 10 July 2022 13:51 )

Read more...

REVIEW Combinational Arithmetic Circuits

Sunday, 19 June 2022 13:31

Semicon Editor 01

I. Introduction I. IntroductionArithmetic circuits are the ones which perform arithmetic operations like addition, subtraction, multiplication, division, parity calculation. Most of the time, designing these circuits is the same as designing muxers, encoders and decoders.

Last Updated ( Monday, 03 April 2023 23:22 )

Read more...

Review SystemC Modules

Sunday, 12 June 2022 23:28

Semicon Editor 01

Â 1. Introduction Modules are the basic building block within SystemC to partition a design. Modules allow designers to break complex systems into smaller more manageable pieces. Â

Last Updated ( Sunday, 12 June 2022 23:31 )

Read more...

REVIEW Structs And Units

Wednesday, 01 June 2022 18:16

Semicon Editor 01

1. Introduction to Structs 1. Introduction to Structs

The basic organization of an e program is a tree of structs. A struct is a compound type that contains data fields, procedural methods, and other members. It is the e equivalent of a class in other object-oriented languages.

Last Updated ( Monday, 03 April 2023 23:24 )

Read more...

Review Conditional Flow Control

Tuesday, 24 May 2022 23:32

Semicon Editor 01

1.  Conditional Flow Control: Conditional flow like in any other programming language is used for controlling execution a block of code, when a condition is true. 2. Content - Conditional Flow Control Part-I

Last Updated ( Tuesday, 24 May 2022 23:36 )

Read more...

Review Digital Combinational Logic

Monday, 16 May 2022 15:12

Semicon Editor 01

1. Digital Logic Families 1. Digital Logic Families

Logic families can be classified broadly according to the technologies they are built with. In earlier days we had vast number of these technologies, as you can see in the list below. DL : Diode Logic.

Last Updated ( Monday, 03 April 2023 23:26 )

Read more...

Review Functional Coverage

Sunday, 08 May 2022 23:52

Semicon Editor 01

1 Introduction to Coverage 1 Introduction to Coverage

Typically in verification flow, we do code coverage, but doing code coverage shows only if all the lines of the DUT is executed, if all the possible cases of a expression are covered.

Last Updated ( Monday, 03 April 2023 23:29 )

Read more...

Review Events And Temporal Expressions

Sunday, 01 May 2022 12:47

1. Temporal Expression Recognition 1. Temporal Expression Recognition

Temporal Expression Recognition (TER) is the process of locating phrases that denote temporal information. Temporal expressions may be an expressed point in time, a duration or a frequency.

Read more...

REVIEW SPECMAN IN ONE DAY

1. About this document This document has three target audiences. Those who are not at all familiar with Specman should find in the first chapter a brief objective account of its main working principles and a discussion of its pros and cons.

Read more...

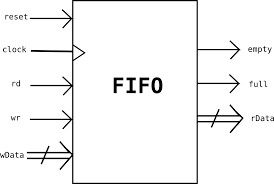

REVIEW VERIFICATION OF FIFO

ABSTRACT An improved technique for fifo design is to perform asynchronous comparisons between the fifo write and read pointers that are generated in

Read more...

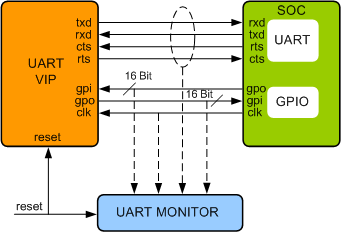

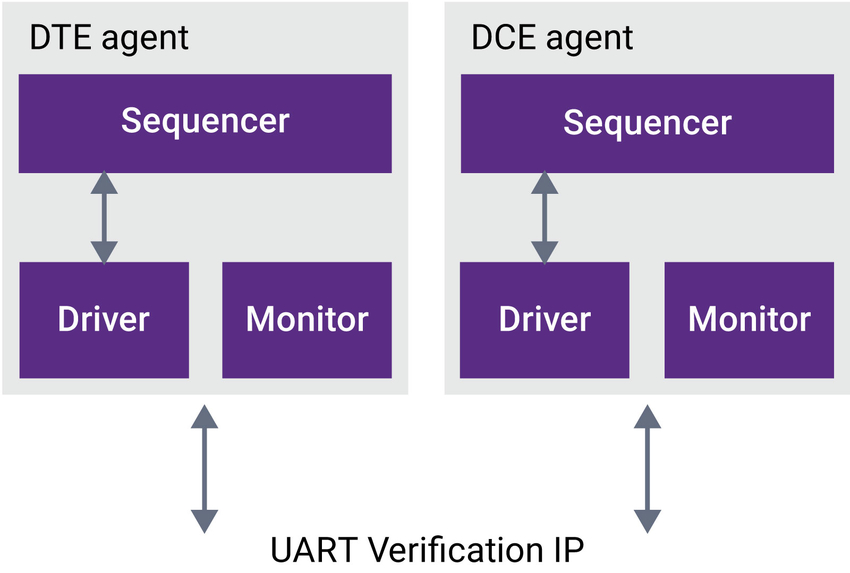

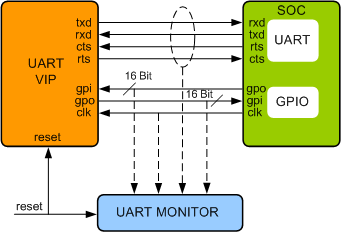

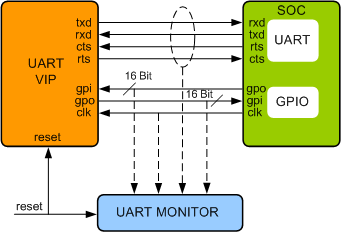

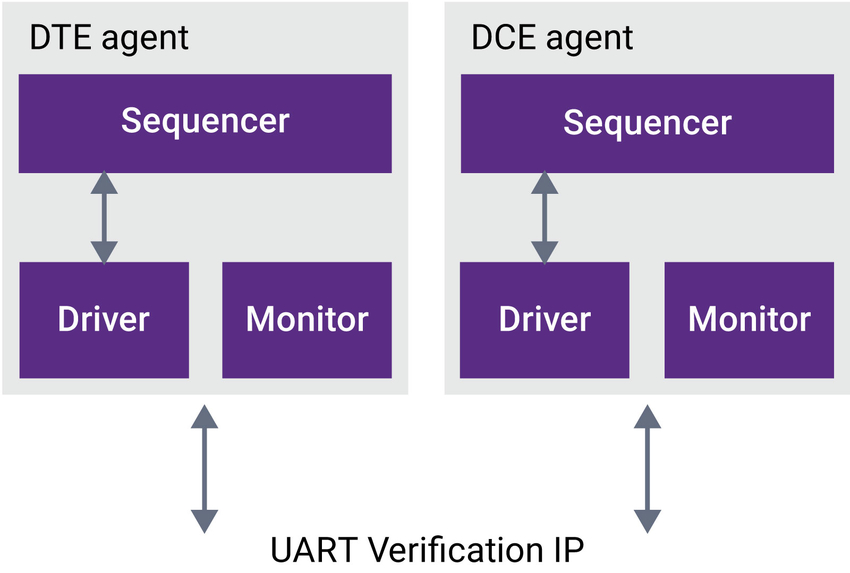

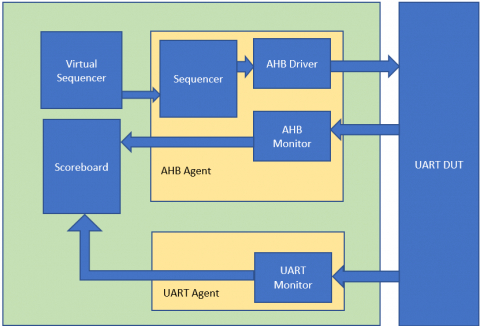

Review Verification Of UART

Sunday, 10 April 2022 18:13

Semicon Editor 01

1. Overview If the designer creates the product, the simulator is the person who ensures that the product has to meet the best quality when it reaches the customer.

Read more...

Review Verification Of UART

Sunday, 10 April 2022 18:13

Semicon Editor 01

1. Overview If the designer creates the product, the simulator is the person who ensures that the product has to meet the best quality when it reaches the customer.

Last Updated ( Tuesday, 03 May 2022 19:35 )

Read more...

Verification Of UART Part - III

Tuesday, 05 April 2022 15:54

Semicon Editor 01

UART Scoreboard 1 <' 2 struct uart_sb {

Last Updated ( Tuesday, 03 May 2022 19:35 )

Read more...

Verification Of UART Part - II

Tuesday, 05 April 2022 15:48

Semicon Editor 01

Device Under Test 1 //----------------------------------------------------- 2 // Design Name : uart

Last Updated ( Tuesday, 03 May 2022 19:36 )

Read more...

|

|

|

|

|

|

|

Page 1 of 118 |

Interrupt handling is a well-known feature of any SoC which usually comprises of CPU, Bus Fabric, several Controllers, Sub-Systems & many IP blocks as part of it. In some way or other Interrupts are used to act as the sideband signals of the Design/IP Blocks & most of the time it’s not the part of the main bus or control bus.

Interrupt handling is a well-known feature of any SoC which usually comprises of CPU, Bus Fabric, several Controllers, Sub-Systems & many IP blocks as part of it. In some way or other Interrupts are used to act as the sideband signals of the Design/IP Blocks & most of the time it’s not the part of the main bus or control bus.