Là thiết bị thao tác các đại lượng vật lý được biểu diễn dưới dạng tương tự. Trong hệ thống tương tự các đại lượng có thể thay đổi trong một khoảng giá trị liên tục. Một vài hệ thống tương tự thường gặp như: bộ khuếch đại âm tần, thiết bị thu phát băng từ,…Tín hiệu tương tự được minh hoạ bằng hình 1.1

1.1.2 Hệ thống số (digital system)

Là tập hợp các thiết bị được thiết kế để thao tác thông tin logic hay đại lương vật lý được biểu diển dưới dạng số, tức là những đại lượng chỉ có giá trị rời rạc. Đây thường là các hệ thống điện tử nhưng đôi khi cũng có hệ thống từ, cơ hay khí nén. Một vài hệ thống kỹ thuật số ta thường gặp là: máy vi tính, máy tính tay, thiết bị nghe nhìn số và hệ thống điện thoại. Tín hiệu số được minh họa như hình 1.2

Mạch số có nhiều ưu điểm hơn so với mạch tương tự do đó mạch số ngày càng có nhiều ứng dụng trong ngành điện tử, cũng như trong hầu hết các lĩnh vực khác.

Một số ưu điểm của kỹ thuật số:

Một số ưu điểm của kỹ thuật số:

- Thiết bị số dễ thiết kế hơn

- Thông tin được lưu trữ và truy cập dễ dàng và nhanh chóng

- Tính chính xác và độ tin cậy cao

- Có thể lập trình hệ thống hoạt động của hệ thống kỹ thuật số.

- Mạch số ít bị ảnh hưởng bởi nhiễu, có khả năng tự lọc nhiễu,tự phát hện sai và sửa sai.

- Nhiều mạch số có thể được tích hợp trên một chíp IC.

- Độ chính xác và độ phân giải cao.

Nhược điểm của kỹ thuật số

Nhược điểm của kỹ thuật số

Hầu hết các đại lượng vật lý có bản chất tương tự, và chính những đại lượng này thường là đầu vào và đầu ra được một hệ thống theo dõi, xử lý và điều khiển. Như vậy muốn sử dụng kỹ thuật số khi làm việc với đầu vào và đầu ra dạng tương tự ta phải thực hiện sự chuyển đổi từ dạng tương tự sang dạng số, sau đó xử lý thông tin số từ ngõ vào và chuyển ngược lại từ dạng số đã xử lý sang dạng tương tự, đây là một nhược điểm lớn của kỹ thuật số.

Để sử dụng được hệ thồng kỹ thuật số đối với đầu vào và đầu ra là dạng tương tự ta cần thực hiện các bước sau đây:

Để sử dụng được hệ thồng kỹ thuật số đối với đầu vào và đầu ra là dạng tương tự ta cần thực hiện các bước sau đây:

![]() Biến đổi thông tin đầu vào dạng tương tự thành dạng số

Biến đổi thông tin đầu vào dạng tương tự thành dạng số

Xử lý thông tin số

Xử lý thông tin số

Biến đổi đầu ra dạng số về lại dạng tương tự

Biến đổi đầu ra dạng số về lại dạng tương tự

Để hiểu được quá trình chuyển đổi đó ta xem ví dụ minh họa hình sau:

Theo sơ đồ khối ở hình 1.3 thì nhiệt độ dưới dạng tương tự được đo, sau đó giá trị đo được sẽ được chuyển sang đại lượng số bằng hệ thống biến đổi tương tự sang số (Analog to Digital Converter – ADC). Đại lượng số này được xử lý qua một mạch số. Đầu ra số được đưa đến bộ biến đổi số sang tương tự (Digital to Analog Converter – DAC), cuối cùng đầu ra tương tự được đưa vào bộ điều khiển để tiến hành điều chỉnh nhiệt độ.

Một nhược điểm khác của hệ thống số đó là giá thành cao, ví dụ như truyền hình số sẽ tốn kém hơn truyền hình tương tự.

1.1.3 Hệ thập phân

Trong các hệ thống số thì hệ thập phân gần gũi nhất vì nó được ta sử dụng hằng ngày. Khi hiểu các đặc điểm của nó sẽ giúp hiểu hơn những hệ thống số khác.

Hệ thập phân – hay còn gọi làhệ cơ số 10. Bao gồm 10 chữ số (ký hiệu) đó là 0, 1, 2, 3, 4, 5, 6, 7, 8, 9.

Hệ thập phân là một hệ thống theo vị trí vì trong đó giá trị của một chữ số phụ thuộc vào vị trí của nó. Để hiểu rõ điều này ta xét ví dụ sau: xét số thập phân 345. Ta biết rằng chữ số 3 biểu thị 3 trăm, 4 biểu thị 4 chục, 5 là 5 đơn vị. Xét về bản chất, 3 mang giá trị lớn nhất trong ba chữ số, được gọi là chữ số có nghĩa lớn nhất (MSD). Chữ số 5 mang giá trị nhỏ nhất, gọi là chữ số có nghĩa nhỏ nhất (LSD).

Để diển tả một số thập phân lẻ người ta dùng dấu chấm thập phân để chia phần nguyên và phần phân số.

Ý nghĩa của một số thập phân được mô tả như sau:

Ví dụ 1: Số 435.568

435.568 = 4x102 + 3x101 + 5x100 + 5x10-1 + 6x10-2 + 8x10-3

Tóm lại, một số thập phân; nhị phân hay thập lục đều là là tổng của các tích giữa các giá trị của mỗi chữ số với giá trị vị trí (còn gọi là trọng số) của nó.

1.1.4 Hệ nhị phân

Trong hệ thống nhị phân (binary system) chỉ có hai giá trị số là 0 và 1. Nhưng có thể biểu diễn bất kỳ đại lượng nào mà hệ thập phân và hệ các hệ thống số khác có thể biểu diễn được, tuy nhiên phải dùng nhiều số nhị phân để biểu diễn đại lượng nhất định.

Tất cả các phát biểu về hệ thập phân đều có thể áp dụng được cho hệ nhị phân. Hệ nhị phân cũng là hệ thống số theo vị trí. Mỗi nhị phân đều có giá trị riêng, tức trọng số, là luỹ thừa của 2. Để biểu diễn một số nhị phân lẽ ta cũng dùng dấu chấm thập phân để phân cánh phần nguyên và phần lẻ.

Ý nghĩa của một số nhị phân được mô tả như sau:

Để tìm giá trị thập phân tương đương ta chỉ việc tính tổng các tích giữa mỗi số (0 hay 1) với trọng số của nó.

Ví dụ2 :

1100.1012 = (1x 23) + (1x 22) + (0x21) + (0x20) + (1x2-1) + (0x2-2) + (1x 2-3 )

= 8 + 4 + 0 + 0 + 0.5 + 0 + 0.125

= 12.125

CÁCH GỌI NHỊ PHÂN

Một con số trong số nhị phân được gọi 1 bit (Binary Digital). Bit đầu (hàng tận cùng bên trái) có giá trị cao nhất được gọi là MSB (Most Significant Bit – bit có nghĩa lớn nhất), bit cuối (hàng tận cùng bên phải) có giá trị nhỏ nhất và được gọi LSB (Least Significant Bit – bit có nghĩa nhỏ nhất).

Số nhị phân có 8 bit được gọi là 1 byte, số nhị phân có 4 bit gọi là nipple. Một nhóm các bit nhị phân được gọi một word (từ) khi số đó có 16 bit, số 32 bit gọi là doubleword, 64 bit gọi là quadword.

Để thuận tiện cho việc chuyển đổi số ta cần phải biết một số lũy thừa nguyên của. .Lũy thừa của 2^10 = 1024 được gọi tắt là 1K (đọc K hay kilo), trong ngôn ngữ nhị phân 1k là 1024 chứ không phải là 1000. Những giá trị lớn hơn tiếp theo như:

211 = 21 . 2 10 = 2K212 = 22 . 210 = 4K

220 = 210 . 210 = 1K . 1K = 1M (Mega)

224 = 24 . 220 = 4. 1M = 4M

230 = 210 . 220 = 1K. 1M = 1G (Giga)

232 = 22 . 230 = 4.1G = 4G

Bảng trị giá của 2n

Biểu đồ thời gian dùng để biểu diễn sự thay đổi theo thời gian của tín hiệu số, đặc biệt là biểu diễn hai hay nhiều tín hiệu số trong cùng một mạch điện hay một hệ thống.

CÁCH ĐẾM NHỊ PHÂN

Cách đếm một số nhị phân được trình bày theo bảng sau

Ví dụ 3:

2 bit ta đếm được 22 = 4 số ( 002 đến 112 )

4 bit ta đếm được 24 = 16 số ( 00002 đến 11112 )

Ở bước đếm cuối cùng, tất cả các bit đều ở trạng thái 1 và bằng 2N – 1 tong hệ thập phân.

Ví dụ: sử dụng 4 bit, bước đếm cuối cùng là 11112 = 24 – 1 = 1510

1.1.5 Hệ thống số bát phân (Octal Number System)

Hệ bát phân có cơ số 8 nghĩa là có 8 ký số : 0, 1, 2, 3, 4, 5, 6, 7, mỗi ký số của số bát phân có giá trị bất ký từ 0 đến 7. Mỗi vị trí ký số của hệ bát phân có trọng số như sau:

1.1.6 Hệ thống số thập lục phân (Hexadecimal Number System)

Hệ thống số thập lục phân sử dụng cơ số 16, nghĩa là có 16 ký số. Hệ thập lục phân dùng các ký số từ 0 đến 9 cộng thêm 6 chữ A, B, C, D, E, F. Mỗi một ký số thập lục phân biểu diễn một nhóm 4 ký số nhị phân.

Ý nghĩa của hệ thống số thập lục phân được mô tả bằng bảng sau:

Mối quan hệ giữa các hệ thống thập lục phân, thập phân và nhị phân được trình bày bằng bảng sau:

CÁCH ĐẾM SỐ THẬP LỤC PHÂN: khi đếm số thập lục phân, mỗi vị trí được tăng dần 1 đơn vị từ 0 cho đến F. khi đếm đến giá trị F, vòng đếm lại trở về 0 và vị trí ký số kế tiếp tăng lên 1. Trình tự đếm được minh họa như dưới đây:0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F, 10, 11, 12, 13,...,1A, 1B,...,20, 21,..,26, 27, 28, 29, 2A, 2B, 2D, 2E, 2F,..., 40, 41, 42 …., 6F8, 6F9, 6FA, 6FB, 6FC, 6FD, 6FE, 6FF,700,….

CỘNG SỐ HEX (THẬP LỤC PHÂN)

Phép cộng số hex được thực hiện giống như cộng thập phân. Sau đây là cách thức để cộng số hex:

![]() Cộng hai ký số hex trong hệ thập phân, tính nhẫm giá trị thập phân tương đương cho những ký số lớn hơn 9

Cộng hai ký số hex trong hệ thập phân, tính nhẫm giá trị thập phân tương đương cho những ký số lớn hơn 9

![]() Nếu tổng nhỏ hơn hoặc bằng 15, có thể biểu diễn trực tiếp ở dạng ký số hex

Nếu tổng nhỏ hơn hoặc bằng 15, có thể biểu diễn trực tiếp ở dạng ký số hex

![]() Nếu tổng lớn hơn hoặc bằng 16, trừ 16 và nhớ 1 đến vị trí ký số kế tiếp.

Nếu tổng lớn hơn hoặc bằng 16, trừ 16 và nhớ 1 đến vị trí ký số kế tiếp.

Sau đây là một số ví dụ cộng các số hex minh họa

- Ở ví dụ 1 ta cộng các LSD (7 và 4) cho ra 11, là B ở hệ hex. Không có số nhớ, cộng 5 và 3 cho ra 8.

- Ở ví dụ 2 ta bắt đầu cộng 8 và A, tính nhẫm A ra giá trị thập phân là 10 . Do đó tổng là 18, số này lớn hơn 16 nên ta trừ cho 16 được 2, viết số 2 và nhớ 1 sang vị trí kế tiếp. Cộng số nhớ cho 4 và 3 ta được tổng là 8.

- Ở ví dụ 3 tổng của C và D xem như 12 + 13 = 2510, số này lớn hơn 16 nên ta trừ cho 16 còn 9, và nhớ 1 sang vị trí kế tiếp. Cộng số nhớ này với B và 3 ta được 1510 đổi sang số hex là F , nhớ 1 sang vị trí kế tiếp. Cộng số nhớ này với 4 và 4 ta được 9, và kết quả cuối cùng là 9F9.

1.2.1 Mã BCD

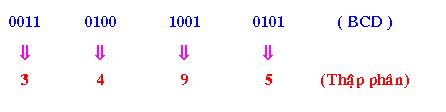

Trực tiếp liên quan đến mạch số (bao gồm các hệ thống sử dụng số) là các số nhị phân nên mọi thông tin dữ liệu dù là số lượng, các chữ , các dấu, các mệnh lệnh sau cùng cũng phải ở dạng nhị phân thì mạch số mới hiểu ra và xử lý được. Do đó phải có quy định cách thức mà các số nhị phân được dùng để biểu thị các dữ liệu khác nhau, kết quả là có nhiều mã số (gọi tắt là mã) được dùng. Trước tiên mã số thập phân thông dụng nhất là mã BCD ( Binary Coded Decimal: mãsố thập phân được mã hóa theo nhị phân ). Sự chuyển đổi thập phân sang BCD và ngược lại gọi là mã hoá và sự lặp mã.

1.2.1.1 Chuyển đổi thập phân sang BCD và ngược lại

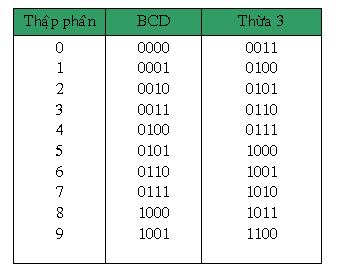

Người ta biểu thị các số thập phân từ 0 đến 9 bởi số nhị phân 4 bit có giá trị như bảng dưới đây.

Chúng ta nên chú ý rằng: mã BCD phải được viết đủ 4 bit và sự tương ứng chỉ được áp dụng cho số thập phân từ 0 đến 9, nên số nhị phân từ 1010 (= 1010) đến 1111 (= 1510) của số nhị phân 4 bit không phải là mã BCD.

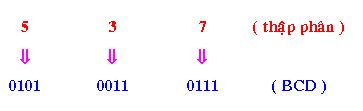

Khi chuyển đổi qua lại giữa thập phân và BCD ta làm như ví dụ minh họa sau đây:

Ví dụ 1: Ðổi 48910 sang mã BCD

Ví dụ 2: Đổi 53710 sang mã BCD

Ví dụ 23: Đổi 00110100100101012 (BCD) sang số thập phân

1.2.1.2 So sánh BCD và số nhị phân

Điều quan trọng là phải nhận ra rằng BCD không phải là hệ thống số như hệ thống số thập phân, nhị phân, bát phân và thập lục phân. Thật ra, BCD là hệ thập phân với từng ký số được mã hóa thành giá trị nhị phân tương đương. Cũng phải hiểu rằng một số BCD không phải là số nhị phân quy ước. Mã nhị phân quy ước biểu diễn số thập phân hoàn chỉnh ở dạng nhị phân; Còn mã BCD chỉ chuyển đổi từng ký số thập phân sang số nhị phân tương ứng.

Mã BCD cần nhiều bit hơn để biểu diễn các số thập phân nhiều ký số (2 ký số trở lên. Điều này là do mã BCD không sử dụng tất cả các nhóm 4 bit có thể có, vì vậy có phần kém hiệu quả hơn.

Ưu điểm của mã BCD là dể dàng chuyển đổi từ thập phân sang nhị phân và ngược lại. Chỉ cần nhớ các nhóm mã 4 bit ứng với các ký số thập phân từ 0 đến 9.

Phối hợp các hệ thống số

Các hệ thống số đã trình bày có mối tương quan như bảng sau đây:

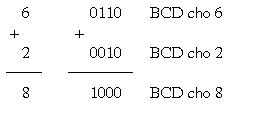

1.2.1.3 CỘNG BCD

Khi tổng nhỏ hơn hoặc bằng 9 thì ta thực hiện phép cộng BCD như cộng nhị phân bình thường.

Ví dụ: xét phép cộng 6 và 2, dùng mã BCD biểu diễn mối ký số

một ví dụ khác, cộng 45 với 33

Tổng lớn hơn 9

ta xét phép cộng 5 và 8 ở dạng BCD:

Tổng của phép cộng ở trên là 1101 không tồn tại trong mã BCD. Điều này xảy ra do tổng của hai ký số vượt quá 9. Trong trường hợp này ta phải hiệu chỉnh bằng cách cộng thêm 6 (0110) vào nhằm tính đến việc bỏ qua 6 nhóm mã không hợp lệ.

Ví dụ:

Một ví dụ khác:

1.2.2 Mã ASCII

Mã chữ số được sử dụng rộng rãi nhất hiện nay là mã ASCII (American Standard Code for Information Interchange). Mã ASCII là mã 7 bit, nên có 27 = 128 nhóm mã, đủ để biểu thị tất cả ký tự của một bàn phím chuẩn cũng như các chức năng điều khiển. Bảng dưới đây minh họa một phần danh sách mã ASCII.

Ký tự | Mã ASCII 7 bit | Bát phân | Thập phân |

| A B C D E F G H I J K L M N O P Q R S T U V W X Y Z 0 1 2 3 4 5 6 7 8 9 <ký tự riêng> . ( + $ * ) _ / , = <RETURN> <LINEFEED> | 100 0001 100 0010 100 0011 100 0100 100 0101 100 0110 100 0111 100 1000 100 1001 100 1010 100 1011 100 1100 100 1101 100 1110 100 1111 101 0000 101 0001 101 0010 101 0011 101 0100 101 0101 101 0110 101 0111 101 1000 101 1001 101 1010 011 0000 011 0001 011 0010 011 0011 011 0100 011 0101 011 0110 011 0111 011 1000 011 1001 010 0000 010 1110 010 1000 010 1011 010 0100 010 1010 010 1001 010 1101 010 1111 010 1100 010 1101 000 1101 000 1010

| 101 102 103 104 105 106 107 110 111 112 113 114 115 116 117 120 121 122 123 124 125 126 127 130 131 132 060 061 062 063 064 065 066 067 070 071 040 056 050 053 044 052 051 055 057 054 075 015 012 | 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53 54 55 56 57 58 59 5A 30 31 32 33 34 35 36 37 30 39 20 2E 28 2B 24 2A 29 2D 2F 2C 2D 0D 0A |

1.2.3 MÃ THỪA 3 (Excess – 3 code)

Bảng dưới đây cho biết mã số thừa 3 ứng với số thập phân từ 0 đến 9. Để chuyển đổi số thập phân sang mã thứa 3 trước tiên ta thêm 3 vào số thập phân đó rồi chuyển sang nhị phân bình thường.

Ví dụ:

210 g 2 + 3 = 510 = 0101

510 g 5 + 3 = 810 = 1000

Do cách viết số thập phân ra mã thừa 3 tương tự như cách viết số thập phân ra mã BCD đã nói ở trước, nên người ta có thể hiểu mã thừa 3 là một dạng của mã BCD. Để dể phân biệt mã BCD đã nói đến ở phần trước được gọi là mã BCD 8421.

1.2.4 MÃ GRAY

Bảng dưới đây trình bày mã số Gray cùng với mã số nhị phân và thập phân từ 0 đến 15. Mã Gray được chọn sao cho chỉ thay đổi một vị trí bit giữa hai mã kế nhau.

1.2.5 THÊM BIT CHẴN LẺ ĐỂ PHÁT HIỆN SAI

Tín hiệu biểu thị số nhị phân truyền từ mạch này sang mạch khác, và nhất là truyền đi xa bị méo dạng và nhiễm nhiễu khiến số nhị phân nhận được có thể sai so với số cần truyền. Để khắc phục hiện tượng này người ta thêm vào mã ASCII 7 bit một bit chẳn lẻ (Parity bit) ở vị trí có nghĩa cao nhất (bên trái) để có dữ liệu 8 bit (1 bit chẵn lẻ, 7 bit dữ liệu gốc). Ở cách dùng lẻ (Odd parity) thì bit parity thay đổi để làm cho tổng số bít 1 trong byte là lẻ. Ví dụ:

Ở cách dùng chẵn (Even parity) thì bit parity thay đổi để cho tổng số bit 1 trong byte là chẵn. Ví dụ:

Bằng các thuật toán, các mạch số sẽ đếm tổng số bit cùng loại trong byte nhận được để xử lý, nếu dữ liệu xử lý không khớp với qui ước về bit chẵn lẻ, số đó sẽ được mạch nhận biết là số bị sai.

CHUYỂN ĐỔI GIỮA CÁC HỆ THỐNG SỐ

1.3.1 ĐỔI TỪ NHỊ PHÂN SANG THẬP PHÂN

Mỗi ký số nhị phân (bit) có một trọng số dựa trên vị trí của nó. Bất kỳ số nhị phân nào cũng đều có thể đổi thành số thập phân tương đương bằng cách cộng các trọng số tại những vị trí có bit 1.

Để hiểu rõ hơn ta xét một vài ví dụ sau đây:

Có hai cách chuyển đổi một số thập phân sang nhị phân tương đương.

Phương pháp thứ nhất là cách đi ngược lại quá trình đổi nhị phân sang thập phân, đó là : số thập phân được trình bày dưới dạng tổng các lũy thừa của 2, sau đó ghi các kí số 0 và 1 vào vị trí bit tương ứng.

Phương pháp thứ nhất là cách đi ngược lại quá trình đổi nhị phân sang thập phân, đó là : số thập phân được trình bày dưới dạng tổng các lũy thừa của 2, sau đó ghi các kí số 0 và 1 vào vị trí bit tương ứng.

Cách thứ hai giúp chuyển đổi từ số thập phân nguyên sang nhị phân là dùng phương pháp lặp lại phép chia cho 2. Ví dụ, với một số thập phân 27 ta thực hiện phép chia số này cho 2 và ghi lại số dư sau mỗi lần chia cho đến khi thu được thương số bằng 0, và kết quả nhị phân hình thành bằng cách viết số dư đầu tiên là LSB và số dư cuối cùng là MSB.

Cách thứ hai giúp chuyển đổi từ số thập phân nguyên sang nhị phân là dùng phương pháp lặp lại phép chia cho 2. Ví dụ, với một số thập phân 27 ta thực hiện phép chia số này cho 2 và ghi lại số dư sau mỗi lần chia cho đến khi thu được thương số bằng 0, và kết quả nhị phân hình thành bằng cách viết số dư đầu tiên là LSB và số dư cuối cùng là MSB.

Lưu đồ trên biểu diển phương pháp lặp lại phép chia để chuyển đổi số nguyên thập phân sang nhị phân. Phương pháp này cũng được sử dụng để chuyển đổi số nguyên thập phân sang bất ký hệ thống số nào khác.

1.3.3 ĐỔI TỪ BÁT PHÂN SANG THẬP PHÂN

Ta dể dàng đổi số bát phân sang thập phân tương đương bằng cách nhân từng ký số bát phân với trọng số của nó, rồi cộng kết quả với nhau.

Ví dụ 7: Đổi số bát phân 4708 thành số thập phân

4758 = 4x(82) + 7x(81) + 5x(80)

= 4x64 + 7x8 + 5x1

= 31710

Ví dụ 8: Đổi số bát phân 34.6 thành số thập phân

34.68 = 3x(81) + 4x(80) + 6x(8-1)

= 24 + 4 + 0.75

= 28.7510

1.3.4 ĐỔI TỪ THẬP PHÂN SANG BÁT PHÂN

Có thể dùng phương pháp lặp lại phép chia để đổi một số nguyên thập phân sang bát phân tương đương, với số chia là 8.

Ví dụ 9: Đổi số thập phân 36510 thành số bát phân tương đương

Chú ý một điều là: số dư đầu tiên là số có giá trị nhỏ nhất (LSB) của số bát phân, số dư cuối cùng là số có giá trị lớn nhất (MSB) của số bát phân.

1.3.5 ĐỔI TỪ BÁT PHÂN SANG NHỊ PHÂN

Phép đổi từ bát phân sang nhị phân đuợc thực hiện bằng cách đổi từng ký số bát phân sang số nhị phân 3 bit tương đương. Tám ký số bát phân được đổi như bảng sau đây:

Ví dụ 10:

Đổi số 3468 sang nhị phân

ð Như vậy số bát phân 3468 tương đương với số nhị phân 0111001102

1.3.6 ĐỔI TỪ NHỊ PHÂN SANG BÁT PHÂN

Đổi từ số nguyên nhị phân sang bát phân được thực hiêïn ngược lại với quá trình đổi từ bát phân sang nhị phân. Các bit của số nhị phân được nhóm thành từng nhóm 3 bit, bắt đầu từ LSB. Sau đó mỗi nhóm được đổi sang số bát phân tương đương.

Ví dụ 11: đổi số nhị phân 1001101102 thành số bát phân

Như vậy số nhị phân 1001101102 tương đương với số bát phân 4668

khi không đủ 3 bit cho nhóm còn lại, trường hợp này ta sẽ thêm một hoặc hai bit 0 vào bên trái MSB của số nhị phân để đủ cho nhóm sau cùng.

Ví dụ 12: đổi số 110111012 thành số bát phân

Cách đếm trong hệ bát phân: trong hệ bát phân ký số lớn nhất là 7 vì vậy trong cách đếm bát phân, vị trí ký số tăng từ 0 đến 7, tiếp đó ta lặp lại từ 0 cho đến vòng kế tiếp và tăng vị trí ký số lên 1.

Như vậy với N vị trí số bát phân thì ta có thể đếm từ 0 đến 8N – 1, tổng cộng có 8N số đếm khác nhau. Ví dụ: với 4 vị trí ký số bát phân ta có thể đếm từ 00008 đến 77778.

1.3.7 ĐỔI TỪ THẬP LỤC PHÂN SANG THẬP PHÂN

Một số thập lục phân có thể được đổi thành số thập phân tương đương dựa vào dữ liệu mỗi vị trí ký số thập lục phân có trọng số là lũy thừa 16. LSD có trọng số là 160, ký số thập lục phân ở vị trí tiếp theo có số mũ tăng lên. Quá trình chuyển đổi như sau:

Ví dụ ta đổi một số thập lục phân 45616 sang số thập phân tương đương ta làm như sau:

45616 = 4x162 + 5x161 + 6x160

= 4x256 + 5x16 + 6x1

= 1024 + 80 + 6

= 111010

Một ví dụ khác đổi số thập lục phân 4BE16 thành số thập phân tương đương

4BE16 = 4x162 + 11x161 + 14x160

= 1024 + 176 + 14

= 121410

Chú ý, trong ví dụ thứ 2 thay 11 vào B và 14 vào E khi đổi sang thập phân.

Theo cách chuyển đổi như 2 ví dụ trên thì ta có thể đổi bất kỳ một số thập lục phân sang thập phân tương đương.

1.3.8 ĐỔI TỪ THẬP PHÂN SANG THẬP LỤC PHÂN

Tương tự như cách đổi từ thập phân sang nhị phân hay bát thân, khi đổi từ thập phân sang thập lục phân ta cũng dùng cách lặp lại phép chia cho 16 và lấy số dư như trước.

Ví dụ 15: đổi số 76510 thành số thập lục phân.

Ta thực hiện phép chia, ta được:

Ví dụ 16: Đổi 72410 thành số thập lục phân

Chúng ta nên nhớ rằng bất kỳ một số dư nào trong phép chia lớn hơn 9 đều được biểu diễn bởi các chữ từ A đến F khi đổi sang số thập lục phân.

1.3.9 ĐỔI TỪ THẬP LỤC PHÂN SANG NHỊ PHÂN

Cách đổi từ số thập lục phân sang số nhị phân cũng giống như đổi từ bát phân sang nhị phân, nghĩa là mỗi ký số thập lục phân được đổi sang giá trị nhị phân 4 bit tương đương.

Ví dụ17: Đổi số 8D216

1.3.10 ĐỔI TỪ NHỊ PHÂN SANG THẬP LỤC PHÂN

Để đổi từ số nhị phân sang thập lục phân ta làm ngược lại cách đổi từ thập lục phân sang nhị phân. Nghĩa là ta nhóm thành từng nhóm 4 bit, mỗi nhóm được đổi sang ký số thập lục phân tương đương. Số 0 có thể được thêm vào để hoàn chỉnh 4 bit cuối cùng.

Ví dụ18: Đổi số 110011011012 thành số thập lục phân

Ví dụ 19: Đổi số 10101001112 thành số thập lục phân

TÓM TẮT CÁC PHÉP CHUYỂN ĐỔI GIỮA CÁC HỆ THỐNG SỐ:

Khi thực hiện phép biến đổi từ hệ nhị phân (hoặc bát phân hay thập lục phân), ta lấy tổng trọng số của từng vị trí ký số.

Khi thực hiện phép biến đổi từ hệ nhị phân (hoặc bát phân hay thập lục phân), ta lấy tổng trọng số của từng vị trí ký số.

Khi đổi từ hệ thập phân sang hệ nhị phân (bát phân hay thập lục phân), ta áp dụng phương pháp lặp lại phép chia cho 2 (8 hay 16) và kết hợp các số dư.

Khi đổi từ hệ thập phân sang hệ nhị phân (bát phân hay thập lục phân), ta áp dụng phương pháp lặp lại phép chia cho 2 (8 hay 16) và kết hợp các số dư.

Khi đổi từ số nhị phân sang bát phân (hay thập lục phân), ta nhóm các bit thành từng nhóm 3 (hoặc 4) bit và đổi từng nhóm này sang ký số bát phân (hay thập lục phân) tương đương.

Khi đổi từ số nhị phân sang bát phân (hay thập lục phân), ta nhóm các bit thành từng nhóm 3 (hoặc 4) bit và đổi từng nhóm này sang ký số bát phân (hay thập lục phân) tương đương.

Khi đổi từ số bát phân (hay thập lục phân) sang nhị phân, ta đổi mỗi ký tự thành số nhị phân 3 (hoặc 4) bit tương đương.

Khi đổi từ số bát phân (hay thập lục phân) sang nhị phân, ta đổi mỗi ký tự thành số nhị phân 3 (hoặc 4) bit tương đương.

Khi đổi từ số bát phân sang thập lục phân (hay ngược lại), ta đổi sang nhị phân trước, sau đó đổi sang hệ thống số mong muốn.

Khi đổi từ số bát phân sang thập lục phân (hay ngược lại), ta đổi sang nhị phân trước, sau đó đổi sang hệ thống số mong muốn.

1.4.1.CỘNG NHỊ PHÂN

Phép cộng hai số nhị phân được tiến hành giống như cộng số thập phân. Các bước của phép cộng nhị phân được áp dụng cho số nhị phân. Tuy nhiên, chỉ có bốn trường hợp có thể xảy ra trong phép cộng hai số nhị phân (bit) tại vị trí bất kỳ. Đó là:

Dưới đây là một vài ví dụ về cộng hai số nhị phân (số thập phân tương đương trong dấu ngoặc):

Phép cộng là phép toán số học quan trọng nhất trong hệ thống kỹ thuật số. Như ta sẽ thấy, các phép trừ, nhân và chia được thực hiện ở hầu hết máy vi tính và máy tính bấm tay hiện đại nhất thực ra chỉ dùng phép cộng làm phép toán cơ bản của chúng.

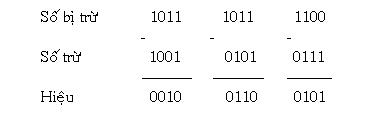

1.4.3 TRỪ NHỊ PHÂN

Trong phép trừ nếu số trừ nhỏ hơn số trừ, cụ thể là khi 0 trừ 1, thì phải mượn 1 ở hàng cao kế và là 2 ở ở hàng đang trừ và số mượn này phải trả lại cho hàng cao kế tương tự như phép trừ của hai số thập phân.

Ví dụ 1: trường hợp trừ hai số nhị phân 1 bit

Ví dụ 2: Trừ hai số nhị phân nhiều bit

1.4.4 BIỂU DIỄN CÁC SỐ CÓ DẤU

Do đa số máy tính xử lý cả số âm lẫn số dương nên cần có dấu hiệu nào đó để biểu thị dấu của số ( + hay - ). Thường thì người ta thêm vào một bit phụ gọi là bit dấu. Thông thường chấp nhận bit 0 là bit dấu biểu thị số dương, bit 1 là bit dấu biểu thị số âm.

Dạng bù 1

Dạng bù 1

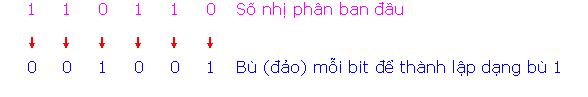

Để có bù 1 của số nhị phân, ta thay mỗi bit 0 thành bit 1 và mỗi bit 1 thành bit 0. Nói cách khác, ta thay đỗi mỗi bit trong số nhị phân đã cho thành bit bù (đảo) tương ứng.

Ví dụ :

Dạng bù 2

Dạng bù 2

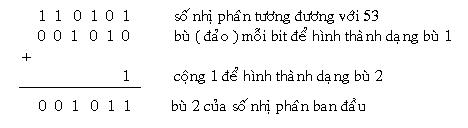

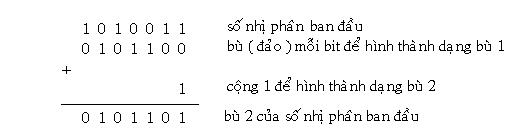

Bù 2 của một số nhị phân được hình thành bằng cách lấy bù 1 của số và cộng 1 vào vị trí nhỏ nhất.

Ví dụ 3: Tìm dạng bù 2 của số 1101012 = 5310

Ví dụ 4:

Biểu diễn số có dấu bằng bù 2

Biểu diễn số có dấu bằng bù 2

Bù 2 biểu diễn những số có dấu theo cách sau đây:

Nếu là số dương, thì trị tuyệt đối được biểu diễn theo dạng nhị phân thực sự của nó, và bit dấu là 0 được đặt vào trước MSB.

Nếu là số âm, trị tuyệt đối được biểu diễn ở dạng bù 2, và bit dấu là 1 được đặt trước MSB.

Ví dụ minh họa:

Các phép tính trong bù 2 tương tự như phép tính số nhị phân bình thường.

1.4.5 NHÂN NHỊ PHÂN

Phép nhân số nhị phân được thực hiện tương tự như nhân số thập phân. Quá trình thật ra đơn giản hơn vì ký số của số nhân chỉ là 0 và 1, vì vậy ta chỉ nhân cho 0 hay 1.

Ví dụ:

1.4.6 CHIA SỐ NHỊ PHÂN

Phép chia một số nhị phân (số bị chia) cho một số khác (số chia) được thực hiện giống như phép chia số thập phân. Tiến trình thức tế còn đơn giản hơn do khi kiểm tra xem có bao nhiêu lần số chia “ đi vào” số bị chia, chỉ có hai khả năng đó là 0 và 1. Quá trình chia được minh họa bằng ví dụ sau:

Trong ví dụ đầu tiên ta có 10012 chia cho 112, tương đương 910 chia cho 310.

Thương số là 00112 = 310. Trong ví dụ thứ 2, 10102 chia cho 1002 tức là 1010 chia cho 410 kết quả là 0010.12 = 2.510.

Phép chia số có dấu được thực hiện như phép nhân. Số âm được biến thành số dương bằng phép bù, sau đó mới thực hiện phép chia. Nếu số bị chia và số chia có dấu ngược nhau, thương số đổi sang số âm bằng cách lấy bù 2 nó và gán bit dấu là 1. Nếu số bị chia và số chia cùng dấu, thương số sẽ là số dương và được gán bit dấu là 0.

2.1.1 CÁC PHÉP TOÁN Ở ĐẠI SỐ BOOLE

Bởi vì các đại lượng chỉ có hai trạng thái nên đại số Boole rất khác đại số thường và dễ tính toán hơn. Ở đại số Boole không có phân số, số thập phân, số ảo, số phức, căn số… mà chỉ thực hiện chủ yếu 3 phép tính toán cơ bản sau:

Phép OR

Phép OR

Phép AND

Phép AND

Phép phủ định NOT

Phép phủ định NOT

Các phép tính trên khi áp dụng cho logic 0 và 1:

2.1.2 THIẾT LẬP BIỂU THỨC LOGIC

Lập hàm logic cho từng cổng ta đã biết cho bất cứ kết nối nào của các cổng. Từ biểu thức biết được ta có thể tính logic ra tương ứng với mỗt tổ hợp logic vào, và lập bảng sự thật của các ngõ vào (biến số) và ngõ ra (hàm). Để tính logic ra tương ứng với một tổ hợp logic và ta thường là tính thẳng trên mạch.

Ví dụ:

Ví dụ với mạch trên với 4 ngõ vào nên ta có tổng cộng 16 tổ hợp vào nên ta phải tính 16 trạng thái ra khác nhau mới lập được bảng sự thật (Truth Table).

2.1.3 THỰC HIỆN MẠCH TỪ BIỂU THỨC LOGIC

Ngược lại với viết biểu thức từ mạch là thực hiện mạch từ biểu thức logic.

Ví dụ cho biểu thức logic cho là:

nhìn vào biểu thức ta thấy ngõ ra là OR của 3 số hạng nên ta thực hiện mỗi số hạng Y trước.

Với số hạng đầu ta dùng AND, số hạng thứ 2 ta ĐẢO C sau đó AND với B, số hạng thứ 3 ta cũng thực hiện tương tự , sau cùng ta OR 3 ba số hạng lại.

___________________

2.2 CÁC ĐỊNH LÝ ĐẠI SỐ BOOLE

Một biến số

Một biến số

Giao hoán

Giao hoán

Phối hợp

Phối hợp

Phân phối

Phân phối

Một số đẳng thức hữu dụng

Một số đẳng thức hữu dụng

Định lý De Morgan

Định lý De Morgan

Các định lý của đại số Boole được chứng minh hay kiểm chứng bằng nhiều cách. Các cách chứng minh hay kiểm chứng này tương đối đơn giản, người đọc có thể tự chứng minh hay kiểm chứng.

Ví dụ 1: Thiết kế mạch dùng hai cổng logic thỏa bảng sự thật sau đây

Giải: Vì ngõ ra bằng 0 chỉ một trường hợp nên ta viết hệ thức logic ở trường hợp này.

Y= 0 khi A= 0 VÀ B = 1 nên  . Để có Y ta đảo

. Để có Y ta đảo  , nên

, nên  .

.

Mạch thực hiện cổng NOT để tạo ra A đảo, tiếp theo là cổng NAND của  và B (hình 1.30a)

và B (hình 1.30a)

Mặt khác ta có thể dựa vào bảng sự thật dể viết hàm logic cho Y và kết quả là  sử dụng các định lý của đại số Boole ta biến đổi và được kết quả cuối cùng là

sử dụng các định lý của đại số Boole ta biến đổi và được kết quả cuối cùng là  (hình 1.30b).

(hình 1.30b).

Ví dụ 2: Chứng tỏ  .

.

Giải:

Vận dụng các công thức ta dể dang biến đổi được:

Một cách chứng minh khác là ta có thể dùng bảng sự thật để chứng minh biểu thức trên.

_______________

2.3 SỰ CHUYỂN ĐỔI GIỮA CÁC LOẠI CỔNG LOGIC

Các cổng logic có thể chuyển dổi qua lại lẫn nhau từ cổng này thành cổng khác. Để thuận tiện cho việc thiết kế mạch logic nên phải chuyển đổi giữa các cổng với nhau, chủ yếu là chuyển đổi AND thành OR và ngược lại, chuyển đổi AND – OR thành NAND – NAND. Đa số các bài toán thiết kế logic đều yêu cầu sử dụng cổng NAND(việc chế tạo cổng NAND đơn giản hơn các cổng khác). Để thuận lợi cho việc chuyển đổi cần phải nắm vững các định lý của đại số Boole và đặc biệt là định lý De Morgan.

Sau đây là một số chuyển đổi giữa các cổng với nhau:

Các định lý Boole giúp đơn giản các biểu thức logic. Việc đơn giản là cần thiết để mạch thiết kế thực hiện đơn giản và kinh tế hơn. Rút gọn biểu thức là vận dụng các định lý từ hàm một biến cho đến hàm nhiều biến và những đẳng thức hữu dụng. Đặt biệt là hai định lý De Morgan giúp ích cho rất nhiều trong việc rút gọn biểu thức logic và cũng là công cụ chính để chuyển đổi các dạng mạch. Để việc rút gọn biểu thức logic và chuyển đổi mạch dể dàng cần phải nắm vững các định lý của đại số Boole và phải thông thạo chuyển đổi giữa các cổng logic.

Ví dụ 3: Rút gọn các biểu thức sau:

Giải:

Ngoài việc rút gọn biểu thức logic bằng đại số boole, còn sử dụng đại số boole để đơn giản mạch logic. Để đơn giản mạch logic ta làm các bước sau:

- Từ mạch logic xác định biểu thức cho ngõ ra của mạch

- Sau khi xác định được hàm ngõ ra, tiến hành rút gọn biểu thức bằng cách dùng các định lý của đại số boole, đặc biệt là sử dụng định lý De Morgan.

- Sau khi được biểu thức mới, chúng ta có được mạch logic mới tương đương với mạch logic đã cho.

Ví dụ 5: Đơn giản mạch ở hình 1.32 (a)

Giải:

Trước tiên ta viết biểu thức logic cho ngõ ra:

Rút gọn biểu thức ta được:

Từ biểu thức vừa rút gọn được ta thành lập được mạch logic mới như hình 1.32b.

_____________________

2.5 THIẾT KẾ LOGIC TỔ HỢP

Khi làm một bài toán thiết kế logic tổ hợp ta cần thực hiện đúng các bước sau đây:

![]() Bước 1: Dựa vào yêu cầu của bài toán đặt ra, chúng ta đặt các biến cho ngõ vào và các hàm của ngõ ra tương ứng.

Bước 1: Dựa vào yêu cầu của bài toán đặt ra, chúng ta đặt các biến cho ngõ vào và các hàm của ngõ ra tương ứng.

![]() Bước 2: Thiết lập bảng sự thật cho ngõ ra và ngõ vào theo yêu cầu của bài toán

Bước 2: Thiết lập bảng sự thật cho ngõ ra và ngõ vào theo yêu cầu của bài toán

![]() Bước 3: Từ bảng sự thật viết ra biểu thức mô tả sự liên hệ logic giữa ngõ ra và các ngõ vào.

Bước 3: Từ bảng sự thật viết ra biểu thức mô tả sự liên hệ logic giữa ngõ ra và các ngõ vào.

Có hai cách viết biểu thức logic cho ngõ ra, hoặc cho trường hợp logic ra bằng 1, hoặc cho trường hợp logic bằng 0 (hai trường hợp này là tương đương nhau).

Cách viết biểu thức thường ở dạng tổng-các-tích và tích-các-tổng.

![]() Bước 4: Áp dụng các định lý của đại số boole để rút gọn biểu thức logic ngõ ra. Sau đó chuyển sang dạng logic khác để thuận lợi hơn cho việc thực hiện mạch logic.

Bước 4: Áp dụng các định lý của đại số boole để rút gọn biểu thức logic ngõ ra. Sau đó chuyển sang dạng logic khác để thuận lợi hơn cho việc thực hiện mạch logic.

![]() Bước 5: Từ biểu thức logic rút gọn được ta chuyển sang mạch logic tương ứng.

Bước 5: Từ biểu thức logic rút gọn được ta chuyển sang mạch logic tương ứng.

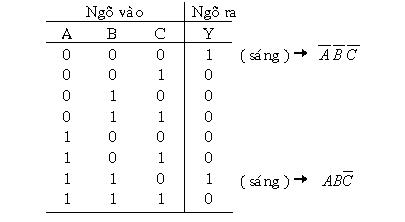

Ví dụ 6:

Một ngôi nhà có 3 công tắc, người chủ nhà muốn bóng đèn sáng khi cả 3 công tắc đều hở, hoặc khi công tắc 1 và 2 đóng còn công tắc thứ 3 hở. Hãy thiết kế mạch logic thực hiện sao cho:

a. Số cổng là ít nhất.

b. Chỉ dùng một cổng NAND 2 ngõ vào.

Giải:

Bước 1:

Gọi 3 công tắc lần lượt là A, B, C. Bóng đèn là Y.

Trạng thái công tắc đóng là logic 1, hở là 0. Trạng thái đèn sáng là logic 1 và tắt là 0.

Bước 2:

Từ yêu cầu bài toán ta có bảng sự thật:

Bước 3: Từ bảng sự thật,ta viết biểu thức ngõ ra theo trường hợp logic 1 vì ngõ ra ở logic 1 xuất hiện ít nhất, như vậy biểu thức tính toán sẽ đơn giản hơn nhiều.

Biểu thức logic ngõ ra

Nếu không rút gọn biểu thức logic ta thực hiện mạch logic thì số cổng logic sử dụng sẽ rất nhiều hình 1.33 (b).

Bước 4: Rút gọn biểu thức logic:

Đến đây thì ta thấy rằng biểu thức logic đã gọn và số cổng logic sử dụng là ít nhất.

Bước 5: Mạch logic tương ứng của biểu thức:  hình 1.33 a

hình 1.33 a

b. biến đổi mạch logic chỉ sử dụng một loại cổng NAND 2 ngõ vào.

Xuất phát từ biểu thức ban đầu, ta sử dụng định lý De Morgan để biến đổi.

Lấy đảo của Y ta được:

Không khai triển  vì đã là một cổng NAND. Biểu thức còn ở dạng tổng nên ta đảo một lần nữa, ta được:

vì đã là một cổng NAND. Biểu thức còn ở dạng tổng nên ta đảo một lần nữa, ta được:

Đến đây ta thấy rằng thừa số trong ngoặc chưa NAND được với C nên ta cần đảo hai lần nữa để được kết quả tất cả đều là cổng NAND 2 ngõ vào:

Từ biểu thức trên ta có sơ đồ mạch logic hình 1.34

_____________

2.6 Ý NGHĨA CỦA KÝ HIỆU LOGIC.

Mạch logic (mạch số) nhận dữ liệu ở các ngõ vào và xuất dữ liệu ở ngõ ra. Dữ liệu là tín hiệu nhị phân chỉ gồm hai mức: mức cao (logic 1) hoặc mức thấp (logic 0). Để thuận lợi cho việc thiết kế mạch logic.

Khi không có vòng tròn nhỏ ở đường vào hay đường ra trên ký hiệu mạch logic, đường đó gọi là kích hoạt (tích cực) ở mức cao (active-HIGH). Còn nếu có vòng tròn nhỏ ở đường vào hay đường ra, đường đó gọi là kích hoạt ở mức thấp (active-LOW). Sự có mặt hay vắng mặt của vòng tròn sẽ quyết định trạng thái kích hoạt ở mức cao/kích hoạt ở mức thấp của đầu ra hay đầu vào, nó cũng được dùng để giải thích hoạt động của mạch.

Sau đây là minh họa bằng cổng NAND (hình 1.35).

Trên ký hiệu này (hình 1.35 (a)) có vòng tròn ở đầu ra, nhưng không có vòng tròn ở đầu vào. Vì vậy đầu ra tích cực ở mức thấp và đầu vào kích hoạt ở mức cao.

Trên ký hiệu hình 1.35 (b) có đầu ra kích hoạt ở mức cao và các đầu vào kích hoạt ở mức thấp.

Vì sao chúng ta phải tìm hiểu ý nghĩa của ký hiệu logic? Lý do là chúng ta sẽ sử dụng ký hiệu thay thế này để biểu vẽ và phân tích logic theo dạng tác động kích hoạt và cách thay thế ký hiệu logic như sau:

Để có ký hiệu thay thế cho một cổng logic, ta hãy lấy ký hiệu chuẩn rồi thay đổi ký hiệu đại số của nó (OR thành AND, hoặc AND thành OR ), và đổi vòng tròn trên cả hai đầu vào lẫn đầu ra.

Để giải thích hoạt động của một cổng logic, ta cần chú ý trạng thái logic nào, 0 hay 1, là trạng thái kích hoạt của đầu vào và đầu ra.

Ví du 7:

Cho ngõ ra của mạch như hình 1.36 a, vẽ lại mạch để mô tả ngõ ra tác động ở mức thấp.

Giải: Vì ngõ ra tác động mức thấp nên thêm vòng tròn phủ định. Do đó đổi OR thành AND với các vòng tròn phủ định ở ngõ vào. Theo quy luật ta thêm vòng tròn phủ định cho ngõ ra của cổng OR và NAND còn cổng NOT thì không vì đã có vòng tròn phủ định. Tiếp theo chuyển đổi cổng OR và NAND để đảm bảo logic (hình 1.36 b).

Trước khi đi vào cấu trúc của mạch TTL cơ bản, xét một số mạch điện cũng có khả năng thực hiện chức năng logic như các cổng logic trong vi mạch TTL:

Mạch ở hình 1.46 hoạt động như một cổng AND. Thật vậy, chỉ khi cả hai đầu A và B đều nối với nguồn, tức là để mức cao, thì cả hai diode sẽ ngắt, do đó áp đầu ra Y sẽ phải ở mức cao. Ngược lại, khi có bất cứ một đầu vào nào ở thấp thì sẽ có diode dẫn, áp trên diode còn 0,6 hay 0,7V do đó ngõ ra Y sẽ ở mức thấp.

Tiếp theo là một mạch thực hiện chức năng của một cổng logic bằng cách sử dụng trạng thái ngắt dẫn của transistor (hình 1.47).

Hai ngõ vào là A và B, ngõ ra là Y.

Phân cực từ hai đầu A, B để Q hoạt động ở trạng thái ngắt và dẫn bão hoà

Cho A = 0, B = 0 Þ Q ngắt, Y = 1

A = 0, B = 1 Þ Q dẫn bão hoà, Y = 0

A = 1, B = 0 Þ Q dẫn bão hoà, Y = 0

A = 1, B = 1 Þ Q dẫn bão hoà, Y = 0

Có thể tóm tắt lại hoạt động của mạch qua bảng dưới đây

Nghiệm lại thấy mạch thực hiện chức năng như một cổng logic NOR

Vì có cấu tạo ở ngõ vào là điện trở, ngõ ra là transistor nên mạch NOR trên được xếp vào dạng mạch RTL

Với hình trên, nếu mạch chỉ có một ngõ vào A thì khi này sẽ có cổng NOT, còn khi thêm một tầng transistor trước ngõ ra thì sẽ có cổng OR

Bây giờ để có cổng logic loại DTL, ta thay hai R bằng hai diode ở ngõ vào (hình 1.48)

Khi A ở thấp, B ở thấp hay cả 2 ở thấp thì diode dẫn làm transistor ngắt do đó ngõ ra Y ở cao.

Khi A và B ở cao thì cả hai diode ngắt => Q dẫn => y ra ở thấp

Rõ ràng đây là 1 cổng NAND dạng DTL (diode ở đầu vào và transistor ở đầu ra)

Các mạch RTL, DTL ở trên đều có khả năng thực hiện chức năng logic nhưng chỉ được sử dụng ở dạng đơn lẻ không được tích hợp thành IC chuyên dùng bởi vì ngoài chức năng logic cần phải đảm bảo người ta còn quan tâm tới các yếu tố khác như :

Tốc độ chuyển mạch (mạch chuyển mạch nhanh và hoạt động được ở tần số cao không).

Tổn hao năng lượng khi mạch hoạt động (mạch nóng, tiêu tán mất năng lượng dưới dạng nhiệt).

Khả năng giao tiếp và thúc tải, thúc mạch khác.

Khả năng chống các loại nhiễu không mong muốn xâm nhập vào mạch, làm sai mức logic.

Chính vì thế mạch TTL đã ra đời, thay thế cho các mạch loại RTL, DTL. Mạch TTL ngoài transistor ngõ ra như ở các mạch trước thì nó còn sử dụng cả các transistor đầu vào, thêm một số cách nối đặc biệt khác, nhờ đó đã đảm bảo được nhiều yếu tố đã đề ra. Hình 1.49 là cấu trúc của một mạch logic TTL cơ bản :

Mạch này hoạt động như một cổng NAND.

Hai ngõ vào là A và B được đặt ở cực phát của transistor Q1 (đây là transistor có nhiều cực phát có cấu trúc mạch tương đương như hình bên )

Hai diode mắc ngược từ 2 ngõ vào xuống mass dùng để giới hạn xung âm ngõ vào, nếu có, giúp bảo vệ các mối nối BE của Q1

Ngõ ra của cổng NAND được lấy ra ở giữa 2 transistor Q3 và Q4, sau diode D0

Q4 và D0 được thêm vào để hạn dòng cho Q3 khi nó dẫn bão hoà đồng thời giảm mất mát năng lượng toả ra trên R4 (trường hợp không có Q4,D0) khi Q3 dẫn.

Điận áp cấp cho mạch này cũng như các mạch TTL khác thường luôn chuẩn là 5V

Mạch hoạt động như sau :

Khi A ở thấp, B ở thấp hay cả A và B ở thấp Q1 dẫn điện; phân cực mạch để áp sụt trên Q1 nhỏ sao cho Q2 không đủ dẫn; kéo theo Q3 ngắt.

Như vậy nếu có tải ở ngoài thì dòng sẽ đi qua Q4, D0 ra tải xuống mass. Dòng này gọi là dòng ra mức cao kí hiệu là IOH

Giả sử tải là một điện trở 3k9 thì dòng là:

Khi cả A và B đều ở cao, nên không thể có dòng ra A và B được, dòng từ nguồn Vcc sẽ qua R1, mối nối BC của Q1 thúc vào cực B làm Q2 dẫn bão hòa.

Nếu mắc tải từ nguồn Vcc tới ngõ ra Y thì dòng sẽ đổ qua tải, qua Q3 làm nó dẫn bão hoà luôn. Ngõ ra sẽ ở mức thấp vì áp ra chính là áp VCE của Q3 khoảng 0,2 đến 0,5V tuỳ dòng qua tải. Khi này ta có dòng ra mức thấp kí hiệu là IOL. Sở dĩ gọi là dòng ra vì dòng sinh ra khi cổng logic ở mức thấp (mặc dù dòng này là dòng chảy vào trong cổng logic)

Ví dụ nếu tải là 470 ohm thì dòng IOL khi này là:

Vậy mạch logic ở trên có chức năng hoạt động như 1 cổng NAND 2 ngõ vào

Nếu để hở hai ngõ vào A và B thì Q1 vẫn ngắt, Q2 vẫn dẫn, kéo theo Q3 dẫn khi có tải ngoài tức là ngõ ra Y vẫn ở cao, do đó giống như trường hợp ngõ A và B nối lên mức cao.

Nếu A và B nối chung với nhau hay Q1 chỉ có 1 cực phát thì mạch NAND chuyển thành mạch NOT

Việc sắp xếp thứ tự Rc, Q4, D0, Q3 thành hình cột giống như hình cột chạm-totem pole-hình tổ vật của người Mĩ da đỏ nên dạng mạch này được gọi là mạch logic ngõ ra cột chạm, cấu trúc của các loại cổng logic khác như and, or, exor cũng giống như vậy. Tuy vậy ta cũng sẽ gặp các mạch logic có ngõ ra kiểu khác như mạch ngõ ra cực thu để hở, ngõ ra ba trạng thái. Những mạch này ta sẽ tìm hiểu ở phần sau. Riêng đối với mạch loại này, khi ngõ ra chuyển tiếp trạng thái từ thấp lên cao có thể xảy ra trường hợp cả Q3 và Q4 cùng dẫn (Q3 chưa kịp tắt). Điều này làm cho dòng bị hút từ nguồn lớn hơn hẳn và có thể làm sụt áp nguồn trong vài ns. Vấn đề này ta cũng sẽ nói kỹ hơn ở bài sử dụng cổng logic.

Mạch ngõ ra cột chạm thuộc loại mạch ra kéo lên tích cực (active pull up) tức là ngõ ra được cấp nguồn thông qua Q4 (linh kiện điện tử tích cực). Còn các mạch khác như RTL, DTL ngõ ra được cấp điện thông qua R (linh kiện điện tử thụ động)

Để tăng tốc độ chuyển mạch cao hơn hẳn loại trên, một số cải tiến mới và công nghệ mới đã được thêm vào

Diode thường được được thay thế bởi diode schottky. Cấu trúc lớp tiếp xúc loại này là Si_Al (chất bán dẫn loại p). Áp ngưỡng chỉ còn 0,35V. Kí hiệu của diode như

Tiếp đến, transistor được mắc thêm diode schottky giữa cực nền và cực thu như hình. kí hiệu của transistor sẽ như hình trên.

Khi này thay vì dẫn bão hoà, transistor sẽ chỉ dẫn gần bão hoà do diode đã dẫn ở khoảng 0,3V rồi. Điều này có nghĩa là transistor sẽ chuyển mạch nhanh hơn.

QUY MÔ TÍCH HỢP

Các mạch cổng logic như trên được tích hợp lại thành một mạch tổ hợp bán dẫn rất rất nhỏ và được đặt vào giữa một vỏ bọc, có dây kim loại nối ra ngoài các chân. Thường thì với mạch cổng nand như ở trên sẽ có bốn mạch như thế được tích hợp trong một vỏ bọc, chúng thuộc loại tích hợp cỡ nhỏ: small scale integration (SSI), một số IC đặc biệt có số cổng lớn hơn một chút hay quy mô phức tạp hơn nên thuộc loại tích hợp cỡ vừa: medium scale integration (MSI). Khi nằm trong IC tích hợp, sự sắp xếp mạch và các chân ra vào cho loại cổng chuẩn này (ví dụ với loại cổng nand) sẽ là:

Có nhiều mạch khác sẽ tích hợp nhiều cổng hơn và tất nhiên thành phần chính của những mạch này sẽ là các transistor và quy mô tích hợp có thể từ hàng trăm đến hàng trăm triệu transistor trên một phiến bán dẫn, chỉ được đặt trong một vỏ bọc không lớn quá vài xen ti mét vuông. Chẳng hạn Các mạch chuyển đổi mã, dồn tách kênh, mạch logic và số học mà chúng ta sẽ tìm hiểu ở phần sau thuộc loại tích hợp cỡ vừa, một số là loại tích hợp cỡ lớn : large scale integration (LSI) vì cấu trúc mạch gồm khoảng từ 12 đến 100 cổng cơ bản (MSI) hay 100 đến 1000 cổng cơ bản (LSI)

Các mạch nhớ, vi điều khiển, vi xử lí, lập trình có thể tích hợp từ hàng ngàn đến hàng triệu cổng logic trong nó và được xếp vào loại tích hợp cỡ rất lớn (VLSI) siêu lớn (ULSI).

3.1 TTL ngõ ra cực thu để hở

Hình 1.56 là cấu trúc của một cổng nand 2 ngõ vào và có ngõ ra cực thu để hở. Nhận thấy trong cấu trúc của mạch không có điện trở hay transistor nối từ cực thu của transistor ra dưới Q3 (transistor nhận dòng ) lên Vcc. Khi giao tiếp tải ta phải thêm bên ngoài mạch một điện trở nối từ ngõ ra Y lên Vcc gọi là điện trở kéo lên (pull up resistor Rp) có trị số từ trên trăm ohm đến vài kilo ohm tuỳ theo tải

Hình 1.56 cấu trúc của 1 cổng nand 2 ngõ vào và có ngõ ra cực thu để hở

Chẳng hạn với mạch cổng nand ở trên ta muốn điều khiển tải là một đèn led, led sáng khi ngõ ra ở mức thấp, vậy điện trở kéo lên có thể được tính toán như sau :

Có thể dùng 270 hay 330 ohm, đây cũng chính là điện trở hạn dòng cho led

Còn khi muốn led sáng ở mức cao thì

Khi này dòng ra sẽ là

Với điện áp đặt trên led bằng áp VCE của Q3, led sẽ tắt

Bây giờ ta sẽ thực hiện nối chung nhiều ngõ ra cực thu để hở lại với nhau (chẳng hạn 3 cổng NAND) xem có gì xảy ra.

Hình 1.57 Cách nối chung nhiều ngõ ra cực thu để hở

Nếu Q3 của cả 3 cổng NAND đều tắt, tức là ngõ ra đều ở cao, chúng nối chung lại với nhau, vậy ngõ ra chung tất nhiên ở cao

Khi một trong 3 cổng NAND có ngõ ra ở thấp (Q3 dẫn) thì sẽ có dòng đổ từ nguồn qua điện trở kéo lên để đi vào cổng not này, vậy ngõ ra nối chung sẽ phải ở thấp, mức thấp này không ảnh hưởng gì đến 2 transistor Q3 của 2 cổng kia cả

Như vậy ngõ ra nối chung này hoạt động như là ngõ ra của 1 cổng AND mà 3 ngõ vào chính là 3 ngõ ra của các cổng nối chung ngõ ra. Đây được gọi là cách nối AND các ngõ ra lại với nhau, ta cũng có thể chuyển qua cách nối NOR theo định lý De Morgan.

Qua hình so sánh ở trên sẽ thấy cách dùng cổng nand thường sẽ tốn kém và phức tạp hơn cách dùng cổng nand cực thu để hở (open colector : CO) mặc dù cả 2 cách đều dùng để thực hiện hàm logic

Tổng quát cách tính điện trở kéo lên

Nói chung khi tính điện trở kéo lên thì phải xem xét đến khả năng chịu dòng của transistor ra cổng cực thu hở cũng như điện thế VOL (max) và VOH (min). Tuỳ theo yêu cầu sử dụng, khi muốn giảm công suất tiêu tán thì có thể giảm giá trị điện trở kéo lên, còn khi muốn tăng tốc độ chuyển mạch thì có thể tăng điện trở kéo lên tuy nhiên giá trị điện trở này phải nằm trong giới hạn giữa Rpmax và Rpmin với

Chẳng hạn với loại TTL chuẩn ra cực thu để hở nối chung lại 4 ngõ với nhau và thúc 3 cổng TTL khác thì

Hình 1.58 Cách kết nối với điện trở kéo lên

_____________

3.2 TTL có ngõ ra 3 trạng thái

TTL có ngõ ra 3 trạng thái (hình 1.59) là TTL có ngõ ra ở tầng cuối cùng là loại 3 trạng thái.

Hình 1.59 Cấu trúc của một loại TTL ngõ ra 3 trạng thái

Có một đường điều khiển C (hay đường cho phép G) và một diode được thêm vào.

Khi C ở cao, diode D không dẫn thì mạch hoạt động bình thường như cổng nand ở trước.

Bây giờ đặt C xuống thấp, chẳng hạn nối mass, lập tức Q1 dẫn, dòng đổ qua R1 xuống mass, mà không đổ vào Q2. Q2 ngắt kéo theo Q3 ngắt. Cùng lúc dòng qua R2 sẽ đổ qua diode D1 xuống mass, tức là Q4 cũng không dẫn.

Trong điều kiện cả Q3 và Q4 đều không dẫn, ngõ ra Y chẳng nối với mass hay nguồn gì cả, tổng trở ngõ ra là rất cao, đây chính là trạng thái thứ 3 của mạch.

Khi này nếu có nối nhiều ngõ ra lại với nhau thì khi ở trạng thái thứ 3, các ngõ ra sẽ không bị ảnh hưởng bởi nhau.

Lợi dụng đặc điểm này ta có thể tạo nên đường bus chung

Hình 1.60 Cách tạo đường bus

Như hình 1.60 cho thấy khi C1, C2, C3 ở mức cao, ngõ ra 3 cồng này ở Z cao, nếu C0 ở mức thấp thì tín hiệu D0 sẽ được đưa tới Y

Khi C1 ở mức thấp còn các C0, C2, C3 ở mức cao thì tín hiệu D1 sẽ được đưa tới Y

Tương tự khi ta đưa đường khiển của cổng nào xuống thấp thì tín hiệu đường đó được đưa lên bus

Tuy nhiên khi đã nối chung các ngõ ra 3 trạng thái lại với nhau thì không nên cho nhiều ngõ điều khiển xuống thấp vì khi này sẽ xảy ra tình trạng tranh chấp bus

Đây có thể coi là một cách ghép kênh dữ liệu, cách này ngày nay đang được sử dụng rộng rãi, đặc biệt trong lĩnh vực máy tính.

Kí hiệu cho mạch có ngõ ra 3 trạng thái là thêm dấu tam giác nhỏ như hình 1.61. Cũng cần lưu ý là ngõ điều khiển C cũng có thể tác động ở mức cao để đặt ngõ ra ở trạng thái tổng trở cao, điều này do công nghệ chế tạo thay đổi mạch thêm một chút.

Hình 1.61 kí hiệu cho mạch ngõ ra 3 trạng thái

________________

3.3 PHÂN LOẠI TTL

TTL bắt đầu bằng mã số 54 hay 74. Mã 54 được dùng trong quân sự hay công nghệ cao nên không trình bày, ở đây chỉ nói đến mã 74 dùng trong dân sự hay thương mại. Theo công nghệ chế tạo, các loại 74 khác nhau bao gồm:

Loại này được ra đời sớm nhất ngay từ năm 1964, là sản phẩm của tập đoàn Texas Instruments. Ngày nay vẫn còn dùng. Loại này dung hoà giữa tốc độ chuyển mạch và mất mát năng lượng (công suất tiêu tán). Nền tảng bên trong mạch thường là loại ngõ ra cột chạm như đã nói ở phần trước. Một số kí hiệu cho cổng logic loại này như 7400 là IC chứa 4 cổng nand 2 ngõ vào, 7404 là 6 cổng đảo,… Cần để ý là khi tra IC, ngoài mã số chung đầu là 74, 2 số sau chỉ chức năng logic, còn có một số chữ cái đứng trước mã 74 để chỉ nhà sản xuất như SN là của Texas Instrument, DM là của National Semiconductor,…TTL loại thường 74XX :

Loại 74LXX có công suất tiêu tán giảm đi 10 lần so với loại thường nhưng tốc độ chuyển mạch cũng giảm đi 10 lần. Còn loại 74HXX thì tốc độ gấp đôi loại thường nhưng công suất cũng gấp đôi luôn. Hai loại này ngày nay không còn được dùng nữa, công nghệ schottky và công nghệ CMOS (sẽ học ở bài sau) đã thay thế chúngTTL công suất thấp 74LXX và TTL công suất cao 74HXX

Hai loại này sử dụng công nghệ schottlky nhằm tăng tốc độ chuyển mạch như đã nói ở phần trước. Với loại 74LSXX, điện trở phân cực được giảm xuống đáng kể so với loại 74SXX nhằm giảm công suất tiêu tán của mạch. 74LSXX được coi là CHỦ LỰC của họ TTL trong những năm 1980 và ngày nay mặc dù không còn là loại tốt nhưng nó vẫn là loại phổ dụng.TTL schottky 74SXX và 74LSXX

Hai loại này được phát triển từ 74SXX và 74LSXX nhưng có thêm nhiều sửa đổi mới trong mạch do đó có nhiều đặc điểm nổi bật hơn hẳn các loại trướcTTL shorttky tiên tiến 74ASXX và 74ALSXX

- Có hoạt động logic và chân ra nói chung là giống như các loại trước

- Giập dao động trên đường dẫn tốt hơn

- Chống nhiễu và ổn định cao hơn trong suốt cả khoảng nhiệt độ chạy

- Dòng ngõ vào giảm đi một nửa

- Sức thúc tải gấp đôi

- Tần số hoạt động tăng lên trong khi công suất tiêu tán lại giảm xuống

Điểm mạnh của nó thì có nhiều nhưng giá thành còn khá cao, nên chúng dùng chưa rộng rãi bằng 74LSXX, thường được dùng trong máy vi tính hay các ứng dụng đòi hỏi tần số cao.

TTL nhanh 74FXX

Đây là loại TTL mới nhất sử dụng kĩ thuật làm mạch tích hợp kiểu mới nhằm giảm bớt điện dung giữa các linh kiện hầu rút ngắn thời gian trễ do truyền, tức tăng tốc độ chuyển mạch. Loại này do hãng Motorola sản xuất và thường được dùng trong máy vi tính nơi cần tốc độ rất rất nhanh.

Bảng sau so sánh một số thông số chất lượng của các loại TTL kể trên

Còn bảng dưới đây tóm tắt các thông số điện thế và dòng điện ở ngõ vào và ngõ ra của các loại TTL kể trên

Theo kiểu ngõ ra, như đã tìm hiểu ở trên TTL gồm loại:

- Ngõ ra cột chạm

- Ngõ ra cực thu để hở

- Ngõ ra 3 trạng thái

Ngoài ra cũng có một số loại TTL được chế tạo dùng cho chức năng riêng như cổng đệm, cổng thúc, cổng nảy schmitt trigger, cổng AOI,...

Cổng đệm cổng thúc: là những cổng mạch logic có cấu trúc không khác mấy các loại cổng logic thông thường nhưng được tích hợp sẵn transistor ở bên trong nhờ đó áp ra lẫn dòng ra đều có thể tăng, ta có thể dùng để giao tiếp với tải có áp lên đến 30V hay dòng lên hàng chục mA

Một số cổng đệm thúc là loại có ngõ ra cực thu để hở cho phép ta chọn điện trở kéo lên phù hợp với tải như đã thấy ở phần trước

Một số cổng đệm thúc là loại có ngõ ra 3 trạng thái, nhiều cổng song song dùng cho truyền dữ liệu, phát thu bus-đệm thúc bus 2 chiều

Nhiều cổng đệm thúc không thực hiện chức năng logic mà đơn giản chỉ để đệm và thúc cho tải

Cổng nảy schmitt trigger: là loại cổng logic cho phép chuyển trạng thái dứt khoát giữa mức cao và mức thấp. Với cổng logic thường khi tín hiệu vào có chuyển tiếp chậm thì tín hiệu ra thường có thể bị rung. Với cổng nảy schmitt thì không. Khi tín hiệu chuyển tiếp từ mức thấp lên mức cao nếu đạt tới 1 áp ngưỡng VT+ thì lập tức tín hiệu ra lên cao. Còn khi tín hiệu chuyển tiếp từ mức cao xuống thấp nếu đạt đến 1 áp ngưỡng VT- thì lập tức tín hiệu ra xuống mức thấp. VT+ phải lớn hơn VT-. Chính sai khác giữa VT+ và VT- còn gọi là độ trễ mà cổng nảy schmitt có thể giảm ảnh hưởng của nhiễu rất nhiều. Cổng nảy schmitt có thể dùng làm mạch chuyển mức tín hiệu từ cảm biến hồng ngoại thành tín hiệu mức logic kích cho mạch đếm trong ứng dụng mạch đếm sự kiện mà ta sẽ tìm hiểu ở chương 3, hay nó cũng có thể dùng để chuyển dạng sóng sin khi đã giảm áp thành song vuông mức TTL.

Hình 1.62 Cổng NOT Schmitt trigger và giản đồ tín hiệu

Cũng chế tạo từ các transistor lưỡng cực, ngoài TTL còn có các dạng mạch khác được sử dụng hạn chế nhưng cũng có những đặc điểm riêng được nói đến ở đây bao gồm :

HTL (high threshold logic) vi mạch số mức ngưỡng cao. HTL có điện áp ngưỡng khá cao khoảng 7 đến 8 V nên mức tạp âm cho phép lớn, sức chống nhiễu sẽ cao nhưng mà tốc độ chuyển mạch của HTL khá chậm so với TTL. HTL được sử dụng ở các thiết bị điều khiển công nghiệp nơi cần độ tin cậy cao mà tốc độ cũng không lớn lắm

HTL (high threshold logic) vi mạch số mức ngưỡng cao. HTL có điện áp ngưỡng khá cao khoảng 7 đến 8 V nên mức tạp âm cho phép lớn, sức chống nhiễu sẽ cao nhưng mà tốc độ chuyển mạch của HTL khá chậm so với TTL. HTL được sử dụng ở các thiết bị điều khiển công nghiệp nơi cần độ tin cậy cao mà tốc độ cũng không lớn lắm

ECL (emitter coupled logic) vi mạch số ghép cực emitter chung. ECL có tốc độ chuyển mạch rất rất nhanh, sức chịu tải lớn, tạp âm bên trong thấp nhưng mức tạp âm cho phép lại nhỏ, mất mát năng lượng lớn, mức điện áp ra thay đổi theo nhiệt độ.

ECL (emitter coupled logic) vi mạch số ghép cực emitter chung. ECL có tốc độ chuyển mạch rất rất nhanh, sức chịu tải lớn, tạp âm bên trong thấp nhưng mức tạp âm cho phép lại nhỏ, mất mát năng lượng lớn, mức điện áp ra thay đổi theo nhiệt độ.

I2C (integrated injection logic ) vi mạch số tích hợp phun

I2C (integrated injection logic ) vi mạch số tích hợp phun

Để thoả mãn nhu cầu về vi mạch cỡ lớn (LSI), người ta cố gắng tăng hết cỡ độ tích hợp của vi mạch. Trên miếng bán dẫn Si (vd 6x6 mm) cần phải đặt được hết mức số phần tử logic. Muốn thế thì, một là mỗi phần tử logic phải đơn giản về mạch và chỉ chiếm diện tích nhỏ, hai là tiêu hao công suất của mỗi phần tử logic phải càng nhỏ để tiêu hao công suất tổng của miếng Si trong giới hạn cho phép. Cổng TTL không thoả mãn điều kiện này.

Đầu những năm 70, I2L được nghiên cứu thành công để sản xuất vi mạch cỡ LSI. Mỗi phần tử logic của I2ØL chỉ chiếm diện tích rất nhỏ, cỡ 0,0026mm2 và dòng điện làm việc chỉ dưới 1nA; độ tích hợp đến 500 cổng /1mm2 ( độ tích hợp của mạch TTL cỡ 20 cổng/1mm2).

Điểm mạnh nổi bật của I2L là đơn giản, áp thấp, dòng cực nhỏ, độ tích hợp cao. Còn điểm yếu chính của nó là tốc độ đóng mở khá chậm và biên độ điện áp ra nhỏ.

Một số IC chứa cổng logic thông dụng:

Loại ngõ ra cột chạm :

7400/LS00 : 4 NAND 2 ngõ vào

7410/LS10 : 3 NAND 3 ngõ vào

7420/LS20 : 2 NAND 4 ngõ vào

7430/LS30 : 1 NAND 8 ngõ vào

7402/LS02 : 4 NOR 2 ngõ vào

7427/LS27 : 3 NOR 3 ngõ vào

7404/LS04 : 6 NOT

7408/LS08 : 4 AND 2 ngõ vào

7411/LS11 : 3 AND 3 ngõ vào

7421/LS21 : 2 AND 4 ngõ vào

7432/LS32 : 4 OR 2 ngõ vào

7425 : 2 OR 4 ngõ vào

7486/LS86 : 4 EXOR 2 ngõ vàoLoại ngõ ra cột chạm, nảy schmitt trigger

74132/LS132 : 4 NAND 2 ngõ vào

7413/LS13 : 2 NAND 4 ngõ vào

7414/LS14 : 6 NOTLoại ngõ ra cực thu để hở :

7401/LS01 : 4 NAND 2 ngõ vào

7403/LS03 : 4 NAND 2 ngõ vào

7412/LS12 : 3 NAND 3 ngõ vào

7422/LS22 : 2 NAND 4 ngõ vào

7405/LS05 : 6 NOT

7409/LS09 : 4 AND 2 ngõ vào

74LS15 : 3 AND 3 ngõ vào

74LS266 : 4 EXOR 2 ngõ vàoLoại đệm ra cột chạm

7437/LS37 : 4 NAND 2 ngõ vào

7440/LS40 : 2 NAND 4 ngõ vào

7428/LS28 : 4 NOR 2 ngõ vàoLoại đệm thúc, ra cực thu để hở

7406 : 6 NOT, áp 30V

7407 : 6 đệm thúc, áp 30V

7417 : 6 đệm thúc, áp 15V

7418 : 6 NOT, áp 15V

7426/LS26 : 4 NAND 2 ngõ vào, áp 15V

7438/LS38 : 4 NAND 2 ngõ vào

7433/LS33 : 4 OR 2 ngõ vàoLoại đệm thúc ra 3 trạng thái

74125/LS125 : 4 đệm, thúc bus

74126/LS126 : 4 đệm, thúc bus

74ls244 : 8 đệm, thúc busLoại đệm, thúc 2 chiều (phát thu)

74LS234 : 4 phát thu

74LS245 : 8 phát thu

Sơ đồ chân ra của một số IC cổng logic hay dùng loại 74 chuẩn

Hình 1.63 Sơ đồ chân của một số IC họ 74

______________

3.4 ĐẶC TÍNH ĐIỆN

Đây là những thông tin đi kèm với IC ở dạng tài liệu để cho việc sử dụng IC chính xác hiệu quả.

Vì có nhiều loại TTL khác nhau nên các đặc tính điện của chúng cũng khác nhau, tuỳ loại. Có thể xem chi tiết ở sách dữ liệu (data book) hay bảng dữ liệu (data sheet),… Có 4 loại đặc tính kĩ thuật của một IC bao gồm:

- Các định trị tối đa tuyệt đối (absolute maximum ratings): đây là những giá trị ngưỡng đỉnh mà không nên vượt qua vì sẽ làm hư IC.

- Các điều kiện hoạt động khuyến cáo (Recommended operating conditions): thường chỉ nói đến áp nuôi Vcc, điện thế ra mức cao VOH, điện thế ra mức thấp VOL, khoảng nhiệt độ. Đây là các trị số cho phép, không nên vượt qua vì sẽ không bảo đảm hoạt động logic bình thường cho các IC.

- Các đặc tính điện (Electrical characteristics) trong khoảng nhiệt độ cho phép: nhiều đặc tính điện cần cho việc sử dụng, thiết kế mạch logic.

- Các đặc tính chuyển mạch (Switching characteristics): thường ghi ở điện thế cấp điện Vcc = 5V và nhiệt độ phòng 20 độ C. Đây là các đặc tính nói đến các trì hoãn cũng như các thời tăng, thời giảm khi chuyển mạch. Các thông số này phụ thuộc vào tải ở ngõ ra nhất là điện dung của tải.

- Các bảng dưới đây liệt kê đặc tính của loạt 74XX và 74LSXX hay được dùng, các đặc tính của các loại khác hay của từng IC cụ thể có thể xem trong bảng dữ liệu của IC

Các định trị tối đa tuyệt đối:

Điện thế cung cấp Vcc : 7 V

Điện thế vào VIOL : 7 V

Khoảng nhiệt độ hoạt động TA : 0 đến 740 độ C

Khoảng nhiệt độ lưu trữ Ts :-65 độ C đến 150 độ C

Các điều kiện hoạt động khuyến cáo:

Trong đó :

Min : trị nhỏ nhất

Nom : trị bình thường

Max : trị lớn nhất

Typ : trị điển hình

Đặc tính điện trong khoảng nhiệt độ hoạt động:

Đặc tính chuyển mạch ở Vcc = 5V TA 25 độ C

Các cổng logic và các mạch logic khác không phải cổng cũng có các đặc tính ngõ vào ngõ ra như trên, tuy nhiên cũng có nhiều cổng, nhiều mạch đặc biệt có đặc tính khác xa.

Cũng nên lưu ý rằng các dòng ra ghi ở trước là dòng khi phải bảo đảm điện thế nằm trong khoảng điện thế quy định, nếu không thì dòng có thể lớn hơn rất nhiều.

Với mỗi một cổng logic hay 1 mạch chứa cổng logic đó, khi đánh giá, sử dụng chúng ta cần quan tâm tới những thông số và đặc tính chính của chúng

2.1 Nguồn nuôi và công suất tiêu tán

Vcc : điện áp nguồn cấp cho IC.

Icc : Dòng điện mà các mạch trong IC tiêu thụ từ nguồn.

Vậy năng lượng mà IC sẽ dùng là P = Vcc.Icc. Với Icc là dòng trung bình khi các cổng hoạt động ở mức cao và mức thấp. Năng lượng này không phải là được sử dụng có ích hết mà sẽ bị mất đi một phần ở dạng nhiệt do phải đốt nóng các điện trở, transistor khi mạch hoạt động, nó được gọi là công suất tiêu tán.

Khi không chuyển mạch, nguồn vẫn phải cung cấp để đảm bảo phân cực cho mạch do đó vẫn có mất mát một ít năng lượng, đó là công suất tĩnh.

Khi hoạt động chuyển mạch, năng lượng bị mất đó được quy về công suất động, nếu tần số càng cao, mạch chuyển mạch càng nhiều thì nó phải lớn lên. Công suất tiêu tán chung sẽ là tổng của hai loại mất mát trên:

P = Ps + Pd

Ps của các cổng logic tính chung khoảng 10mW

Công suất tiêu tán được nói đến để đánh giá chất lượng của IC, rõ ràng nếu mạch logic nào có nó thấp thì được đánh giá cao hơn, nhưng cũng có một tiêu chuẩn khác cần quan tâm là tốc độ chuyển mạch của cổng.

2.2 Tốc độ chuyển mạch

Ta biết rằng cấu tạo của cổng logic cũng chỉ là các linh kiện điện tử, transistor ngắt dẫn cần phải có thời gian do đó nếu ngõ vào của cổng logic thay đổi trạng thái thì chắc chắn ngõ ra không thể thay đổi ngay được, thời gian đó rất nhỏ, được gọi là thời gian chuyển tiếp và sai biệt về thời gian giữa sự thay đổi logic ngõ ra so với ngõ vào được gọi là trì hoãn truyền

Đặc tính chuyển mạch của 1 cổng NOT mạch TTL được minh hoạ như hình vẽ sau

Trong đó :

tPHL : thời gian chuyển tiếp cạnh xuống

tPLH : thời gian chuyển tiếp cạnh lên

Khi trì hoãn truyền tPHL hay tPLH bằng đúng nửa chu kì tín hiệu thì cổng logic sẽ không còn tác dụng nữa (chẳng hạn với cổng NOT sẽ không còn đảo chính xác được). Điều này đặt giới hạn lên tần số thay đổi dữ liệu ngõ vào gọi là tần số tín hiệu tối đa fmax .

Ta có fmax = 1/2tPLH

Điều này có nghĩa là fmax càng cao thì cổng càng chuyển mạch tốt, nhanh, nhưng nếu vượt qua fmax (giá trị quy định trong tờ dữ liệu của nhà sản xuất) thì mạch sẽ hoạt động sai logic.

Để đánh giá chính xác giữa các loại cổng người ta đã liên kết cả hai đặc tính công suất tiêu tán và tốc độ chuyển mạch lại thành tích số tốc độ - công suất. Nếu tích này càng nhỏ thì cổng càng tốt và thích hợp với nhiều ứng dụng tốc độ cao hay công suất tiêu tán thấp hay cả hai.

_______________

2.3 Tham số về áp và dòng

VIH (min): điện áp đầu vào mức cao, mức áp nhỏ nhất mà cổng logic có thể hiểu là mức cao (1).

VIL (max): điện áp đầu vào mức thấp, mức áp lớn nhất mà cổng logic có thể hiểu là mức thấp (0) ở ngõ vào.

VOH (min): điện thế đầu ra ở mức cao, mức áp nhỏ nhất mà cổng logic cho ra khi ở mức cao.

VOL (max): điện thế đầu ra ở mức thấp, mức áp lớn nhất mà cổng logic cho ra khi ở mức thấp.

IIH: dòng điện đầu vào mức cao, là dòng sinh ra khi đầu vào cổng logic đang ở cao.

IIL: dòng điện đầu vào mức thấp, là dòng sinh ra khi đầu vào cổng logic đang ở thấp.

IOH: dòng điện đầu ra mức cao, là dòng sinh ra khi đầu ra cổng logic đang ở cao.

IOL: dòng điện đầu ra mức thấp, là dòng sinh ra khi đầu ra cổng logic đang ở thấp.

Các giá trị điển hình của các dòng áp vào ra của một cổng logic loại chuẩn có thể được tóm tắt như hình sau:

Lưu ý về chiều dòng điện nếu mang dấu “–“ thì tức là chỉ dòng chảy ra từ mạch. Giá trị các dòng điện thường thay đổi theo tải, nếu vượt quá trị điển hình (chẳng hạn IOH vượt quá 0,4mA thì áp mức cao VOH sẽ bị tụt xuống dưới 2,4V rơi vào vùng bất định, và khi này mạch có thể không hiểu được mức logic ngõ ra đó là cao hay thấp, tức là hoạt động logic sẽ bị sai.

_____________

2.4 Tính chống nhiễu :

Đôi khi các điện áp và dòng điện vào ra cổng logic đã được đảm bảo ngoài vùng bất định nhưng mạch vẫn có thể hoạt động sai logic, đó là do ảnh hưởng của nhiễu gồm nhiễu từ bên ngoài thâm nhập vào (sấm sét, đóng tắt cầu dao điện, bugi xe, đèn tube khởi động...) tạo điện từ trường cảm ứng vào mạch hay nhiễu phát sinh ra chính bên trong mạch đặc biệt là các xung nhọn xuất hiện trên đường tiếp điện trong mạch do các chuyển tiếp mạch tạo nên. Chính những nhiễu biên độ âm hay dương này chồng lên mức logic 0 hay 1 có thể làm điện thế toàn thể thay đổi lớn tạo ra sự nhầm lẫn giữa logic 0 và 1.

Chính vì thế mà các cổng logic cũng được so sánh ở khả năng chống lại nhiễu này còn gọi là đặc tính kháng nhiễu. Ta tính đến nó ở trường hợp không có tải, giao tiếp giữa 2 cổng logic

Hiệu VOH (min) – VIH (min) gọi là lề nhiễu mức cao VNH

Hiệu VIL (max) – VOL (max) gọi là lề nhiễu mức thấp VNL

Ví dụ 1: Chẳng hạn 1 cổng logic có thông số như bảng sau :

Thì lề nhiễu được tính như sau :

VNH = VOH(min) – VIH(min) = 2,4V – 2V = 0,4V

VNL = VIL(max) – VOL(max) = 0,8V – 0,4V = 0,4V

Ví dụ 2: cho các thông số của 1 dạng cổng 74LSXX, tính toán lề nhiễu cho mạch :

__________________

2.5 Hệ số tải (số toả ra: Fan Out)

Các thông số dòng áp vào ra này cũng còn liên quan tới một thông số khác đó là hệ số tải fan out, tức là với áp ra như vậy thì cồng logic này có thể lái được tối đa bao nhiêu cổng logic cùng loại khác. Với loạt TTL thường thì fan out là 10, với các loại TTL khác nhau thì fan out khác nhau đơn cử một cổng logic TTL có thông số như sau:

IOH(max) = 400uA

IOL(min) = 8mA

IIH(max) = 20uA

IIL(min) = 100mA

Thì số toả ra ở mức cao là 400uA/20uA = 20

Số toả ra ở mức thấp là 8mA/100uA = 80

Vậy số toả ra chung sẽ là 20 nghĩa là 1 cổng logic loại này sẽ thúc được 20 cổng logic khác cùng loại với nó.

Hệ số tải và các thông số dòng áp vào ra ở trên được coi là thông số nền tảng để tính toán sự giao tiếp giữa các mạch TTL khác loại hay giữa một TTL và các mạch logic khác như CMOS.

Một vấn đề nữa cần đặt ra ở đây là liệu có thể nối chung ngõ ra cột chạm của nhiều cổng chung lại với nhau hay không? Việc nối chung một số ngõ ra lại với nhau là để tạo logic mới và cũng để giải quyết việc truyền nhiều tín hiệu logic, từng lúc một đến một nút chung để rồi từ đó đi các nơi. Hãy xét một trường hợp cụ thể như hình 1.55 dưới đây :

Hình 1.55 cách nối hai cổng

Ở hình trên, ngõ ra của 2 cổng được nối chung lại. Xem trường hợp ngõ ra của mạch A ở cao, ngõ ra của mạch B ở thấp, lúc bấy giờ thì 2 transistor Q4A và Q3B dẫn mạnh khiến dòng điện qua chúng có thể vượt trên vài chục mA làm chúng nóng lên hay hư. Tình huống như trên sẽ xấu hơn khi có nhiều ngõ hơn nối lại với nhau. Nếu transistor không bị hư, hệ thức logic giữa các ngõ vào và ngõ ra chung cũng không đảm bảo.

Vì lí do này các nhà sản xuất đã làm ra 2 loại mạch TTL khác cho phép nối chung các ngõ ra lại với nhau ,đó là mạch TTL với ngõ ra cực thu để hở (with open collector output) và mạch TTL với ngõ ra 3 trạng thái (three state output hay tri state output).

Công nghệ MOS (Metal Oxide Semiconductor-kim loại oxit bán dẫn) có tên gọi xuất xứ từ cấu trúc MOS cơ bản của một điện cực nằm trên lớp oxit cách nhiệt, dưới lớp oxit là đế bán dẫn. Transistor trong công nghệ MOS là transistor hiệu ứng trường, gọi là MOSFET (metal oxide silicon field effect transistor). Có nghĩa điện trường ở phía điện cực kim loại của lớp oxit cách nhiệt có ảnh hưởng đến điện trở của đế. Phần nhiều IC số MOS được thiết kế hết bằng MOSFET, không cần đến linh kiện nào khác.

Ưu điểm chính của MOSFET là dễ chế tạo, phí tổn thấp, cỡ nhỏ, tiêu hao rất ít điện năng. Kĩ thuật làm IC MOS chỉ rắc rối bằng 1/3 kĩ thuật làm IC lưỡng cực (TTL, ECL,...). Thêm vào đó, thiết bị MOS chiếm ít chỗ trên chip hơn so với BJT, thông thường, mỗi MOSFET chỉ cần 1 mi li vuông diện tích chip, trong khi BJT đòi hỏi khoảng 50 mi li vuông. Quan trọng hơn, IC số MOS thường không dùng các thành phần điện trở trong IC, vốn chiếm quá nhiều diện tích chip trong IC lưỡng cực. Vì vậy, IC MOS có thể dung nạp nhiều phần tử mạch trên 1 chip đơn hơn so với IC lưỡng cực. Bằng chứng là ta sẽ thấy MOS dùng nhiều trong vi mạch tích hợp cỡ LSI, VLSI hơn hẳn TTL. Mật độ tích hợp cao của IC MOS làm chúng đặc biết thích hợp cho các IC phức tạp, như chip vi xử lí và chip nhớ. Sửa đổi trong công nghệ IC MOS đã cho ra những thiết bị nhanh hơn 74, 74LS của TTL, với đặc điểm điều khiển dòng gần như nhau. Do vậy, thiết bị MOS đặc biệt là CMOS đã đã được sử dụng khá rộng rãi trong mạch MSI mặc dù tốc độ có thua các IC TTL cao cấp và dễ bị hư hỏng do bị tĩnh điện.

Mạch số dùng MOSFET được chia thành 3 nhóm là:

- PMOS dùng MOSFET kênh P

- NMOS dùng MOSFET kênh N tăng cường

- CMOS (MOS bù) dùng cả 2 thiết bị kênh P và kênh N

Các IC số PMOS và NMOS có mật độ đóng gói lớn hơn (nhiều transistor trong 1 chip hơn) và do đó kinh tế hơn CMOS. NMOS có mật độ đóng gói gần gấp đôi PMOS. Ngoài ra, NMOS cũng nhanh gần gấp 2 lần PMOS, nhờ dữ kiện các điện tử tự do là những hạt tải dòng trong NMOS, còn các lỗ trống (điện tích dương chuyển động chậm hơn) là hạt tải dòng cho PMOS. CMOS rắc rối nhất và có mật độ đóng gói thấp nhất trong các họ MOS, nhưng nó có điểm mạnh là tốc độ cao hơn và công suất tiêu thụ thấp hơn. IC NMOS và CMOS được dùng rộng rãi trong lĩnh vực kĩ thuật số, nhưng IC PMOS không còn góp mặt trong các thiết kế mới nữa. Tuy nhiên MOSFET kênh P vẫn rất quan trọng bởi vì chúng được dùng trong mạch CMOS.

Trước khi đi vào công nghệ CMOS ta hãy tìm hiểu qua về NMOS. Cũng cần phải biết rằng PMOS tương ứng cũng giống hệt NMOS, chỉ khác ở chiều điện áp.

Hình 1.64 là cấu tạo của 1 cổng NOT loại NMOS cơ bản

Mạch gồm 2 MOSFET: Q2 làm chuyển mạch còn Q1 làm tải cố định và luôn dẫn, điện trở của Q1 khoảng 100 kW

Ngõ vào mạch đặt ở cực G của Q2, còn ngõ ra lấy ở điểm chung của cực S Q1 và cực D Q2. Nguồn phân cực cho mạch giả sử dùng 5V.

Khi Vin = 5 V, ngõ vào mức cao kích cho Q2 dẫn, trở trên Q2 còn khoảng 1K cầu phân áp giữa RQ1 và RQ2 cho phép áp ra còn khoảng 0,05V tức là ngõ ra ở mức thấp

Khi Vin = 0V, ngõ vào ở mức thấp, Q2 ngắt, trở trên nó khá lớn khoảng 1010 ohm. Cầu phân áp RQ1 và RQ2 sẽ đặt áp ngõ ra xấp xỉ nguồn, tức là ngõ ra ở mức cao.

Vậy mạch hoạt động như một cổng NOT. Cổng NOT được xem là mạch cơ bản nhất của công nghệ MOS. Nếu ta thêm Q3 mắc nối tiếp và giống với Q2 thì sẽ được cổng NAND. Nếu ta mắc Q3 song song và giống với Q2 thì sẽ được cổng NOR. Cổng AND và cổng OR được tạo ra bằng cách thêm cổng NOT ở ngõ ra của cổng NAND và cổng NOR vừa được tạo ra.

Như đã nói ở trước, NMOS không phải để tạo ra các cổng mà thường dùng để xây dựng mạch tổ hợp, mạch tuần tự quy mô thường cỡ MSI trở lên, nhưng tất cả những mạch đó về cơ bản vẫn chỉ là tổ hợp của các mạch cổng logic được kể ra ở đây.

Một số đặc điểm của NMOS :

Tốc độ chuyển mạch: chậm hơn so với loại TTL do điện trở đầu vào khá cao đồng thời bị ảnh hưởng bởi tải dung tính mà nó thúc

Giới hạn nhiễu khoảng 1,5V với nguồn 5V và sẽ tăng tỉ lệ khi nguồn cấp tăng. Như vậy là tính kháng nhiễu kém hơn TTL

Hệ số tải: về lí thuyết là rất lớn do trở đầu vào của mạch rất lớn, tuy nhiên, nếu tần số hoạt động càng cao (trên 100KHz) thì điện dung sinh ra có thể làm suy giảm thời gian chuyển mạch kéo theo giảm khả năng giao tiếp tải. So với TTL thì NMOS vẫn có hệ số tải cao hơn hẳn trung bình là 50 cổng cùng loại.

Công suất tiêu tán: Đây là ưu điểm nổi bật của logic MOS. Thật vậy, chẳng hạn với cổng NOT ở trên khi đầu vào thấp RQ1 = 100k, RQ2 = 1010ohm nên dòng tiêu thụ I = V/R = 0,5nA => P =U.I = 2,5nW

Khi đầu vào cao RQ1 = 100k, RQ2 1k nên dòng tiêu thụ I = V/R = 50uA Þ 0,25mW

Vậy công suất trung bình chỉ cao hơn 0,1 mW một chút, so với TTL thì nó quá nhỏ.

Chính nhờ ưu điểm này mà CMOS có thể tích hợp cỡ LSI và VLSI, nơi mà nhiều cổng, nhiều flip flop, nhiều mạch khác được tích hợp trong một chíp mà không sinh ra nhiệt lớn làm hỏng chip.

Cũng cần lưu ý là logic MOS do đều được xây dựng từ các transistor MOSFET nên rất nhạy tĩnh điện, ở phần sau ta sẽ đề cập chi tiết đến vấn đề này.

___________

Hoạt động của mạch cũng tương tự như ở NMOS

Khi ngõ vào (nối chung cực cổng 2 transistor) ở cao thì chỉ có Q1 dẫn mạnh do đó áp ra lấy từ điểm chung của 2 cực máng của 2 transistor sẽ xấp xỉ 0V nên ngõ ra ở thấp.

Khi ngõ vào ở thấp Q1 sẽ ngắt còn Q2 dẫn mạnh, áp ra xấp xỉ nguồn, tức ngõ ra ở mức cao.

Để ý là khác với cổng NOT của NMOS, ở đây 2 transistor không dẫn cùng một lúc nên không có dòng điện từ nguồn đổ qua 2 transistor xuống mass nhờ đó công suất tiêu tán gần như bằng 0. Tuy nhiên khi 2 transistor đang chuyển mạch và khi có tải thì sẽ có dòng điện chảy qua một hay cả 2 transistor nên khi này công suất tiêu tán lại tăng lên.

Trên nguyên tắc cổng đảo, cũng giống như trước bằng cách mắc song song hay nối tiếp thêm transistor ta có thể thực hiện được các cổng logic khác (hình 1.66). Chẳng hạn mắc chồng 2 NMOS và mắc song song 2 PMOS ta được cổng NAND. Còn khi mắc chồng 2 PMOS và mắc song song 2 NMOS ta được cổng NOR.

2.2 Phân loại

Có nhiều loại IC logic CMOS với cách đóng vỏ (package) và chân ra giống như các IC loại TTL. Các IC có quy mô tích hợp nhỏ SSI vỏ DIP (dual inline package): với hai hàng chân thẳng hàng 14 hay 16 được dùng phổ biến.

CMOS cũ họ 4000, 4500

CMOS cũ họ 4000, 4500Hãng RCA của Mỹ đã cho ra đời loại CMOS đầu tiên lấy tên CD4000A. Về sau RCA có cải tiến để cho ra loạt CD4000B có thêm tầng đệm ra, sau này hãng lại bổ sung thêm loạt CD4500, CD4700.

Hãng Motorola (Mỹ) sau đó cũng cho ra loạt CMOS MC14000, MC14000B, MC14500 tương thích với sản phẩm cũ của RCA.

Đặc điểm chung của loạt này là :

Loại 74CXX

Loại 74CXX

Đây là loại CMOS được sản xuất ra để tương thích với các loại TTL về nhiều mặt như chức năng, chân ra nhưng khoản nguồn nuôi thì rộng hơn. Các đặc tính của loại này tốt hơn loại CMOS trước đó một chút tuy nhiên nó lại ít được sử dụng do đã có nhiều loại CMOS sau đó thay thế loại CMOS tốc độ cao 74HCXX và 74HCTXX. Đây là 2 loại CMOS được phát triển từ 74CXX.

74HCXX có dòng ra lớn và tốc độ nhanh hơn hẳn 74CXX, tốc độ của nó tương đương với loại 74LSXX, nhưng công suất tiêu tán thì thấp hơn. Nguồn cho nó là từ 2V đến 6V.

Còn 74HCTXX chính là 74HCXX nhưng tương thích với TTL nhiều hơn như nguồn vào gần giống TTL : 4,5V đến 5,5V. Do đó 74HCTXX có thể thay thế trực tiếp cho 74LSXX và giao tiếp với các loại TTL rất bình thường.

Ngày nay 74HC và 74HCT trở thành loại CMOS hay dùng nhất mà lại có thể thay thế trực tiếp cho loại TTL thông dụng.

Loại CMOS tiên tiến 74AC, 74ACT

Loại CMOS tiên tiến 74AC, 74ACT

Loại này được chế tạo ra có nhiều cải tiến cũng giống như bên TTL, nó sẽ hơn hẳn các loại trước đó nhưng việc sử dụng còn hạn chế cũng vẫn ở lí do giá thành còn cao.

Chẳng hạn cấu trúc mạch và chân ra được sắp xếp hợp lí giúp giảm những ảnh hưởng giữa các đường tín hiệu vào ra do đó chân ra của 2 loại này khác với chân ra của TTL.

Kháng nhiễu, trì hoãn truyền, tốc độ đồng hồ tối đa đều hơn hẳn loại 74HC, 74HCT.

Kí hiệu của chúng hơi khác một chút như 74AC11004 là tương ứng với 74HC04. 74ACT11293 là tương ứng với 74HCT293.

Loại CMOS tốc độ cao FACT

Loại CMOS tốc độ cao FACT

Đây là sản phẩm của hãng Fairchild, loại này có tính năng trội hơn các sản phẩm tương ứng đã có.

Loại CMOS tốc độ cao tiên tiến 74AHC, 74AHCT

Loại CMOS tốc độ cao tiên tiến 74AHC, 74AHCT

Đây là sản phẩm mới đã có những cải tiến từ loại 74HC và 74HCT, chúng tận dụng được cả 2 ưu điểm lớn nhất của TTL là tốc độ cao và của CMOS là tiêu tán thấp do đó có thể thay thế trực tiếp cho 74HC và 74HCT.

Bảng sau cho phép so sánh công suất tiêu tán và trì hoãn truyền của các loại TTL và CMOS ở nguồn cấp điện 5V.

- Điện áp nguồn cung cấp từ 3V đến 18V mà thường nhất là từ 5 đến 15 V.

- Chúng có công suất tiêu hao nhỏ

- Riêng loại 4000B do có thêm tầng đệm ra nên dòng ra lớn hơn, kháng nhiễu tốt hơn mà tốc độ cũng nhanh hơn loại 4000A trước đó.

- Tuy nhiên các loại trên về tốc độ thì tỏ ra khá chậm chạp và dòng cũng nhỏ hơn nhiều so với các loại TTL và CMOS khác. Chính vì vậy chúng không được sử dụng rộng rãi ở các thiết kế hiện đại.

Ngoài các loại trên công nghệ CMOS cũng phát triển một số loại mới gồm:

BiCMOS

Đây là sản phẩm kết hợp công nghệ lưỡng cực TTL với công nghệ CMOS nhờ đó tận dụng được cả 2 ưu điểm của 2 cộng nghệ là tốc độ nhanh và công suất tiêu tán thấp. Nó giảm được 75% công suất tiêu tán so với loại 74F trong lúc vẫn giữ được tốc độ và đặc điểm điều khiển tương đương. Nó cũng có chân ra tương thích với TTL và hoạt động ở áp nguồn 5V. Tuy nhiên Bi CMOS thường chỉ được tích hợp ở quy mô vừa và lớn dùng nhiều trong giao diện vi xử lí và bộ nhớ, như mạch chốt, bộ đệm, bộ điều khiển hay bộ thu phát.

Loại CMOS điện thế thấp

Đây là loại CMOS khá đặc biết có áp nguồn giảm xuống chỉ còn khoảng 3V. Khi áp giảm sẽ kéo theo giảm công suất tiêu tán bên trong mạch nhờ đó mật độ tích hợp của mạch tăng lên, rồi tốc độ chuyển mạch cũng tăng lên điều này rất cần thiết trong các bộ vi xử lí bộ nhớ ... với quy mô tích hợp VLSI. Cũng có khá nhiều loại CMOS áp thấp, và đây là xu hướng của mai sau, ở đây chỉ nói qua về một số loại của hãng Texas Instruments

74LV (low voltage) : là loạt CMOS điện thế thấp tương ứng với các vi mạch số SSI và MSI của các công nghệ khác. Nó chỉ hoạt động được với các vi mạch 3,3V khác

74LVC (low voltage CMOS ) : gồm rất nhiều mạch SSI và MSI như loạt 74. Nó có thể nhận mức 5V ở các ngõ vào nên có thể dùng để chuyển đổi các hệ thống dùng 5V sang dùng 3,3V khác. Nếu giữ dòng điện ở ngõ ra đủ thấp để điện thế ngõ ra nằm trong 1 giới hạn cho phép, nó cũng có thể giao tiếp với các ngõ vào TTL 5V. Tuy nhiên áp vào cao của các CMOS 5V như 74HC hay 74AHC khiến chúng không thể điều khiển từ các vi mạch LVC

74ALVC (advanced low voltage CMOS ) : là loạt CMOS điện thế thấp, chủ yếu để dùng cho các mạch giao diện bus hoạt động ở 3,3V

74LVT (low voltage BiCMOS) : giống như 74LVC có thể hoạt động ở logic 5V và có thể dùng như mạch số chuyển mức 5V sang 3V

Bảng sau so sánh một số đặc tính của các loại CMOS áp thấp

CMOS cực máng hở, CMOS ra 3 trạng thái và CMOS nảy schmitt trigger

Tương tự như bên TTL, các cổng CMOS cũng có các loại ra hở mảng, ra 3 trạng thái và nảy schmitt trigger, vì có nhiều loại CMOS được sản xuất để tương thích và thay thế cho loại TTL tương ứng.

CMOS racực máng hở

Do dùng MOSFET nên ngõ ra không phải là cực thu mà là cực máng

Ở hình 1.67 trrình bày hai cổng NOT CMOS thường có ngõ ra nối chung với nhau

Nếu 2 đầu vào ở cao thì 2P ngắt, 2N dẫn ngõ ra mức cao bình thường.

Nếu 2 đầu vào ở thấp thì 2P dẫn, 2N ngắt ngõ ra mức thấp bình thường.

Nhưng nếu ngõ vào cổng 1 ở thấp còn ngõ vào cổng 2 ở cao thì P1 dẫn N1 ngắt, P2 ngắt N2 dẫn áp ngõ ra sẽ là nửa áp nguồn Vdd. Áp này rơi vào vùng bất định không thể dùng kích các tải được hơn nữa với áp Vdd mà cao, dòng dẫn cao có thể làm tiêu 2 transistor của cổng.

Vậy cách để cực D ra hở là hợp trong trường hợp này. Trong cấu trúc mạch sẽ không còn MOSFET kênh P nữa, còn MOSFET kênh N sẽ để hở cực máng D. Ta có thể nối các ngõ ra theo kiểu nối AND hay OR và tất nhiên là cũng phải cần điện trở kéo lên để tạo mức logic cao, giá trị của R kéo lên tính giống như bên mạch loại TTL.

CMOS ra 3 trạng thái

Tương tự mạch bên TTL, mạch có thêm ngõ điều khiển G (hay C).

G ở cao 2 cổng nand nối, nên Y = A, ta có cổng đệm không đảo

G ở thấp ngõ ra của 2 cổng nand lên cao làm PMOS và NMOS cùng ngưng dẫn và đây là trạng thái thứ 3 hay còn gọi là trạng thái trở kháng cao (high Z), lúc bấy giờ từ ngõ ra Y nhìn ngược vào mạch thì mạch như không có (điện trở ngõ ra Y lên nguồn và xuống mass đều rất lớn).

Ngõ G cũng có thể tác động ở mức thấp

Kí hiệu logic của mạch

Cổng nảy schmitt trigger tương tự nảy schmitt trigger bên mạch TTL

Cổng truyền dẫn CMOS (transmission gate :TG)

Cổng truyền dẫn CMOS (transmission gate :TG)

Đây là loại cổng logic mà bên công nghệ lưỡng cực không có; cổng truyền dẫn hoạt động như một công tắc đóng mở (số) để cho phép dữ liệu (dạng số) truyền qua lại theo cả 2 chiều.

Trước hết là cấu tạo của cổng truyền NMOS

Tín hiệu truyền có thể là tương tự hay số miễn nằm trong khoảng 0 đến Vdd. Nhưng ở đây để dẽ minh hoạ ta giả sử lấy nguồn cấp là 10V, áp ngưỡng của NMOS sẽ là 2V

Khi ngõ vào ở thấp, tụ sẽ không được nạp nên tất nhiên ngõ ra cũng là mức thấp

Khi ngõ vào ở cao mà đường khiển G vẫn ở thấp thì ngõ ra cũng vẫn ở thấp

Khi ngõ vào ở cao và G ở cao => NMOS dẫn với áp ngưỡng 2V nên tụ nạp đầy đến 8V thì NMOS ngắt, ngõ ra có thể hiểu là mức cao, do đó tín hiệu đã được truyền từ trái sang phải

Khi này mà ngõ vào xuống mức thấp thì tụ sẽ xả qua NMOS do đó ngõ ra lên cao trở lại tức là dữ liệu đã truyền từ phải sang trái

Tuy nhiên ta có nhận xét là, khi bị truyền như vậy dữ liệu đã giảm biên độ đi mất 2V. Với mạch số có thể vẫn hiểu là mức cao mức thấp, còn với mạch tương tự thì như vậy là mất mát năng lượng nhiều rồi, và nó còn bị ảnh hướng nặng hơn khi nhiều cổng truyền mắc nối tiếp nhau.

Cổng truyền CMOS :

Hình 1.70 cho thấy cấu trúc của 1 cổng truyền CMOS cơ bản dùng 1 NMOS và 1PMOS mắc song song, cũng với những giả sử như ở trên bạn sẽ thấy CMOS khắc phục được điểm dở của NMOS và chính nó đã được sử dụng rộng rãi ngày nay.

Khi G ở cao, nếu ngõ vào ở thấp ngõ ra không có gì thay đổi.

Còn nếu ngõ vào ở cao thì cả 2 transistor đều dẫn dữ liệu truyền tù trái sang phải nạp cho tụ, ngõ ra ở mức cao nhưng có 1 điểm khác ở đây là khi tụ nạp đến 8V thì NMOS ngắt trong khi PMOS vẫn dẫn mạnh làm tụ nạp đủ 10V.

Khi ngõ ra đang ở 10V, ngõ G vẫn ở cao mà ngõ vào xuống thấp thì tụ sẽ xả ngược trở lại qua 2 transistor làm ngõ vào lên cao trở lại.

Các kí hiệu cho cổng truyền như hình

________________

2.3 Đặc tính kỹ thuật