Sequential Circuits Part-I

Monday, 06 December 2021 21:08

Semicon Editor 01

Introduction

Digital electronics is classified into combinational logic and sequential logic. Combinational logic output depends on the inputs levels, whereas sequential logic output depends on stored levels and also the input levels

Last Updated ( Tuesday, 31 May 2022 17:29 )

Read more...

|

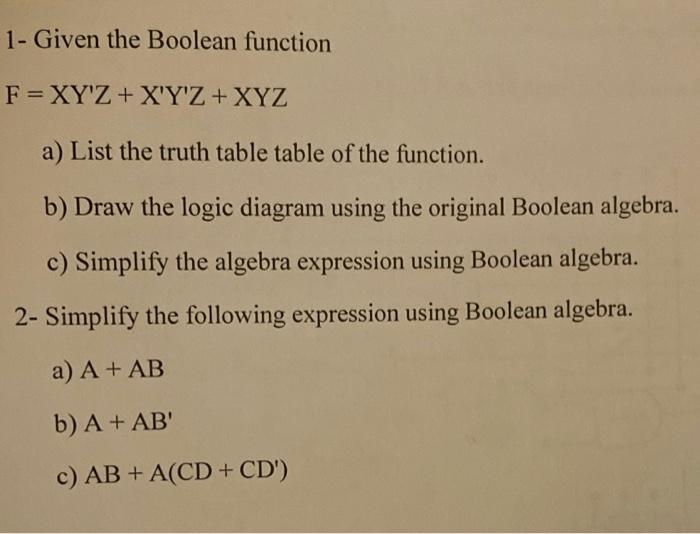

Simplification Of Boolean Functions Part-IV

Monday, 06 December 2021 20:56

Semicon Editor 01

QUINE-McCLUSKEY MINIMIZATION

Quine-McCluskey minimization method uses the same theorem to produce the solution as the K-map method, namely X(Y+Y')=X

Last Updated ( Tuesday, 29 March 2022 00:38 )

Read more...

Simplification Of Boolean Functions Part-III

Saturday, 04 December 2021 13:14

Semicon Editor 01

4-Variable K-Map There are 16 cells in a 4-variable (W, X, Y, Z); K-map as shown in the figure below.

Last Updated ( Tuesday, 29 March 2022 00:38 )

Read more...

Simplification Of Boolean Functions Part-II

Saturday, 04 December 2021 12:56

Semicon Editor 01

2-Variable K-Map In any K-Map, each square represents a minterm. Adjacent squares always differ by just one literal (So that the unifying theorem may apply: X + X' = 1). For the 2-variable case (e.g.: variables X, Y), the map can be drawn as below.

Last Updated ( Tuesday, 29 March 2022 00:38 )

Read more...

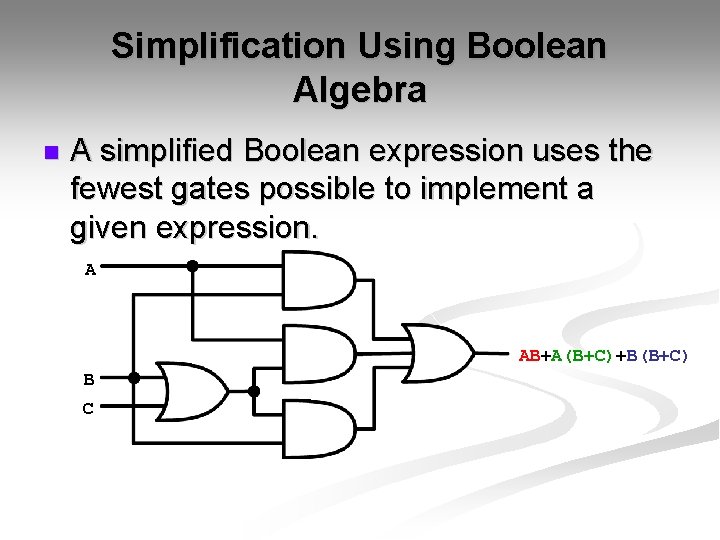

Simplification Of Boolean Functions Part-I

Saturday, 04 December 2021 12:45

Semicon Editor 01

Introduction

Simplification of Boolean functions is mainly used to reduce the gate count of a design. Less number of gates means less power consumption, sometimes the circuit works faster and also when number of gates is reduced, cost also comes down.

Last Updated ( Tuesday, 29 March 2022 00:38 )

Read more...

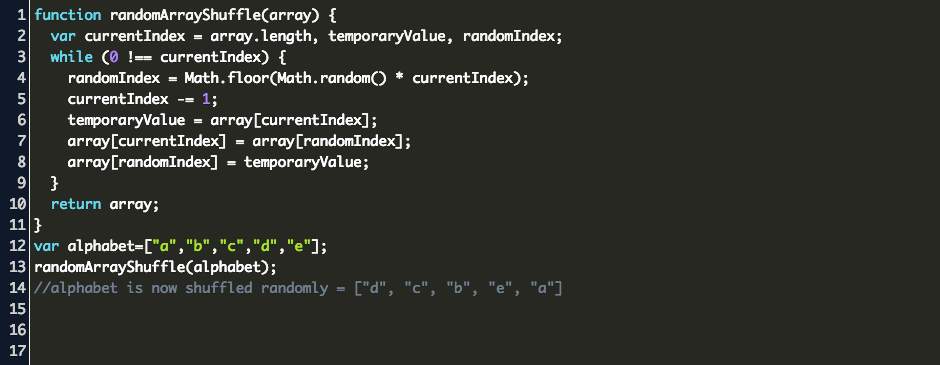

GENERATE THE ARRAY OF UNIQUE VALUES WITHOUT USING RANDOM AND CONSTRAINTS

Tuesday, 30 November 2021 13:32

Semicon Editor 01

Without using Random variable and constraint, you can generate array of random unique values using below code, but it is not fully random.

Last Updated ( Tuesday, 29 March 2022 00:40 )

Read more...

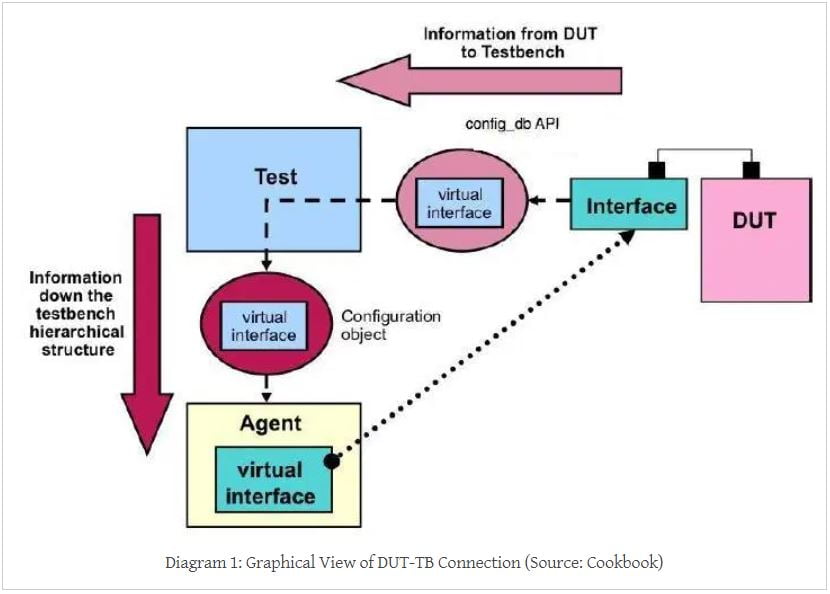

HOW VIRTUAL INTERFACE CAN BE PASS USING UVM_CONFIG_DB IN THE UVM ENVIRONMENT?

Tuesday, 30 November 2021 13:28

Semicon Editor 01

How to connect the DUT to the UVM Testbench?? In our traditional directed Testbench environments, all the components are “static” in nature & information (data/control)

Last Updated ( Tuesday, 29 March 2022 00:39 )

Read more...

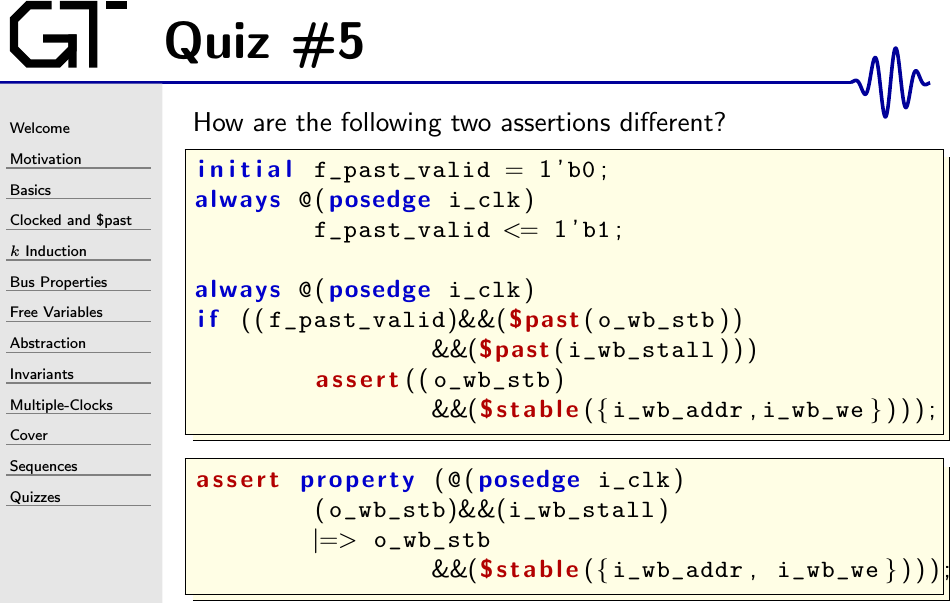

IMMEDIATE VS CONCURRENT ASSERTIONS

Tuesday, 30 November 2021 13:26

Semicon Editor 01

Immediate assertions use expressions and are executed like a statement in a procedural block. They are not temporal in nature and are evaluated immediately when executed. Immediate assertions are used only in dynamic simulations. Following is an example of a simple immediate assertion that checks “if x and y are always equal”:

Last Updated ( Tuesday, 29 March 2022 00:39 )

Read more...

ASSERTIONS AND ADVANTAGES OF ASSERTIONS

Saturday, 27 November 2021 21:45

Semicon Editor 01

An assertion is used to validate the behavior of the design. If the property that is being checked for in a simulation does not behave as per specification, then the assertion fails.

Last Updated ( Tuesday, 29 March 2022 00:39 )

Read more...

UVM_CONFIG_DB AND UVM_RESOURCE_DB

Saturday, 27 November 2021 21:37

Semicon Editor 01

uvm_resource_db: uvm_resource_db is base class and uvm_config_db is extended from uvm_resource_db. Using the resource_db requires that the scope (arbitrary string) for the set and get a match.

Last Updated ( Tuesday, 29 March 2022 00:38 )

Read more...

Process In SystemC Part VI

Saturday, 27 November 2021 21:31

Semicon Editor 01

Local Watching

Local watching allows you to specify exactly which section of the process is watching which signals, and where the event handlers are located.

Last Updated ( Tuesday, 29 March 2022 00:41 )

Read more...

Process In SystemC Part V

Thursday, 25 November 2021 14:24

Semicon Editor 01

Global Watching SC_CTHREAD processes typically have infinite loops that will continuously execute. A designer typically wants some way to initialize the behavior of the loop or jump out of the loop when a condition occurs.

Last Updated ( Tuesday, 29 March 2022 00:41 )

Read more...

Process In SystemC Part IV

Thursday, 25 November 2021 14:20

Semicon Editor 01

dont_initialize()

Process and threads (not the cthreads) get executed automatically in Constrcutor even if event in sensitivity list does not occur. To prevent this unintensional execution, use dont_initialize() function as shown in example.

Last Updated ( Tuesday, 29 March 2022 00:41 )

Read more...

Process In SystemC Part III

Thursday, 25 November 2021 14:19

Semicon Editor 01

Clocked Threads

SC_CTHREAD process is different from the SC_THREAD process in a number of ways. First the SC_CTHREAD process specifies a clock object.

Last Updated ( Tuesday, 29 March 2022 00:41 )

Read more...

Process In SystemC Part II

Thursday, 25 November 2021 14:16

Semicon Editor 01

Threads Threads are second kind of process, which when called keeps executing or waiting for some event to occur. Conditions that enable this processes can be event triggered, like posedge of clock.

Last Updated ( Tuesday, 29 March 2022 00:41 )

Read more...

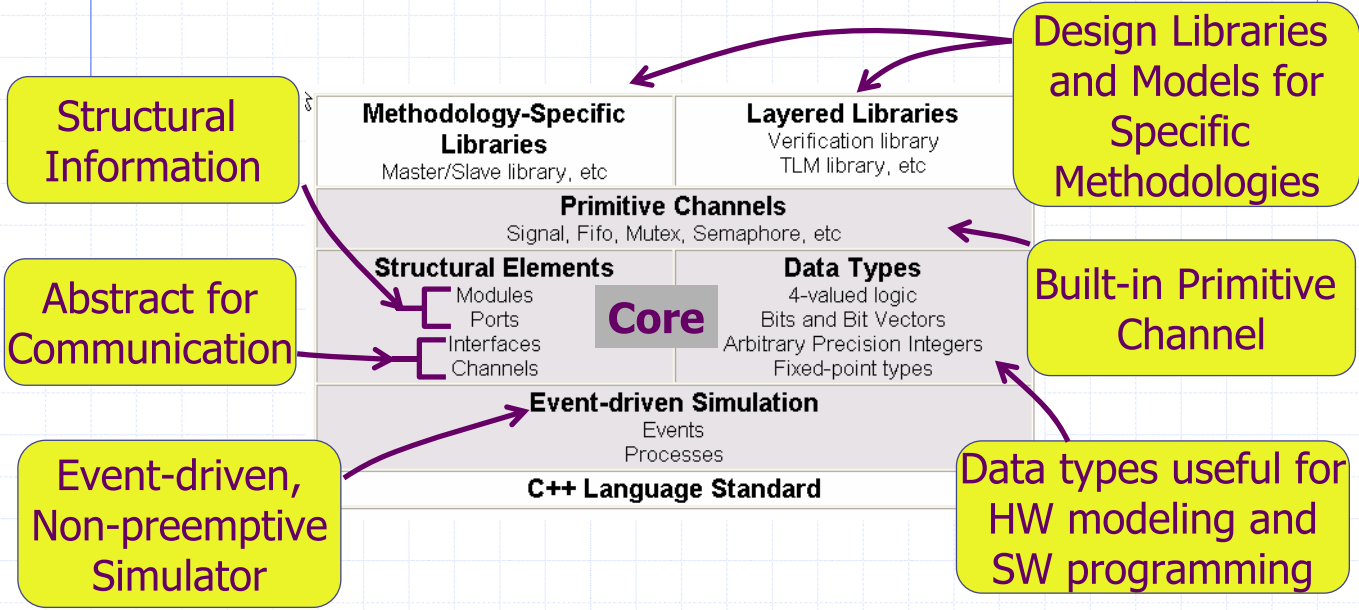

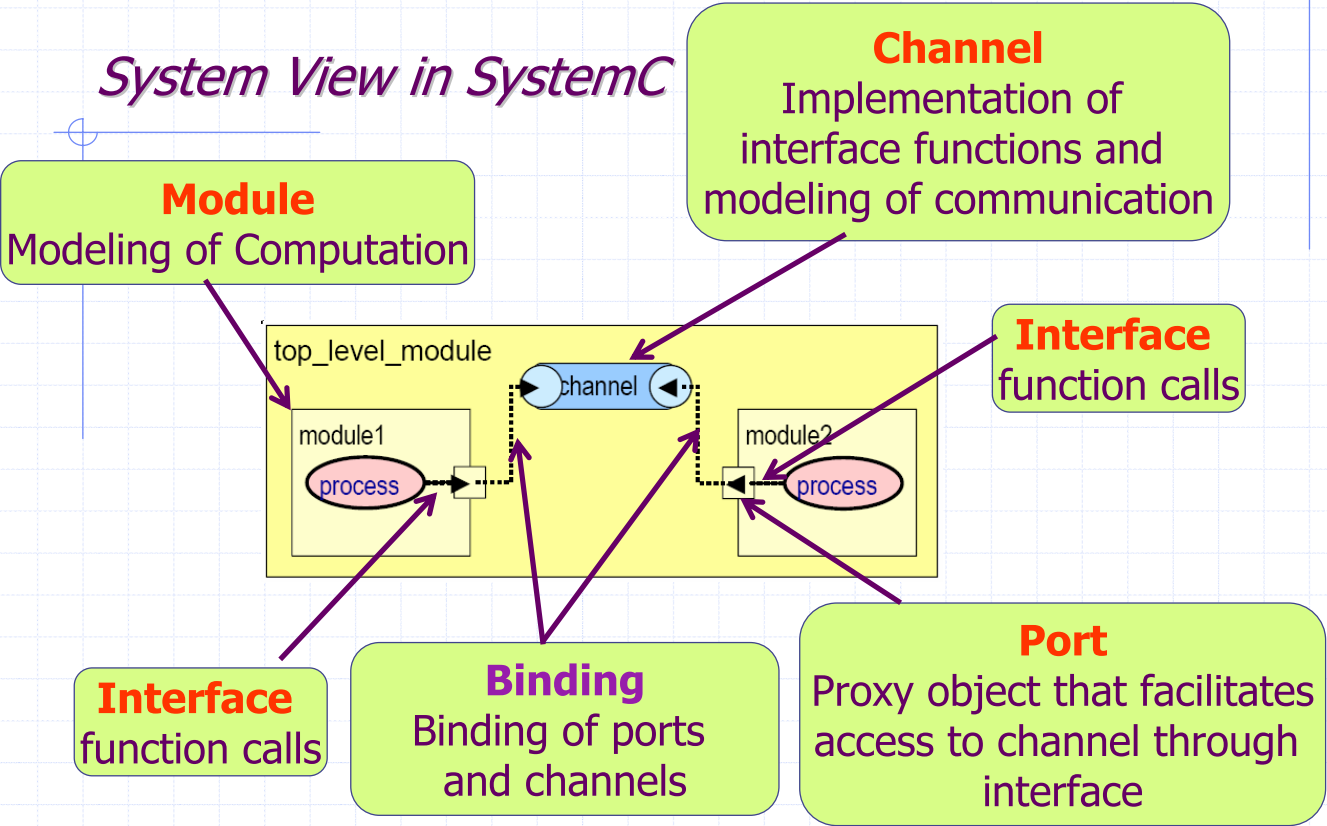

Process In SystemC

Thursday, 25 November 2021 14:13

Semicon Editor 01

Introduction We saw in last chapter basic introduction to Processes. There are three types of processes in SystemC. Processes are not hierarchical, so no process will call another process directly.

Last Updated ( Tuesday, 29 March 2022 00:41 )

Read more...

|

|

|

|

|

|

|

Page 7 of 118 |