It is necessary to manage most of the verification tasks, such as generating stimulus and collecting coverage data, at the transaction level, which is the natural way of verification engineers tend to think of the activity of a system.

UVM provides a set of transaction-level communication interfaces and channels that you can use to connect components at the transaction level.

TLM models are at a higher level of abstraction, and more closely match the level of abstraction at which the verification engineers or design engineers thinks about the intended functionality. This makes it easier to write the models and easier for other engineers to understand them.

Let’s understand this concept with a basic example.

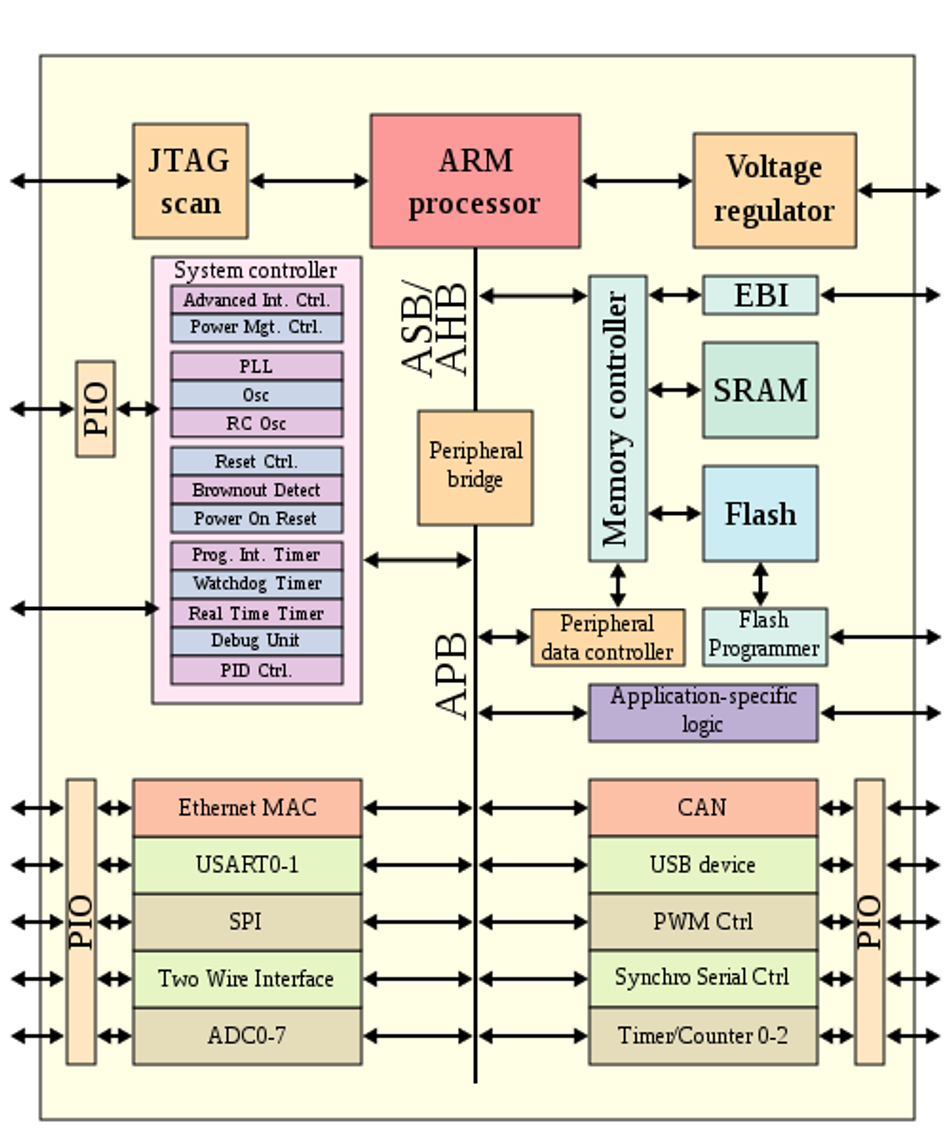

In Transaction Level Modelling, different components or modules communicate using transaction objects. A TLM port defines a set of methods (API) used for a particular connection while the actual implementation of these methods are called TLM exports.

A connection between the TLM port and the export establishes a mechanism of communication between two components.

uvm_blocking_put_port

Producer:

Consumer:

Connection:

In above mentioned example of how a producer can communicate to a consumer using a simple TLM port. The producer can create a transaction and “put” to the TLM port, while the implementation of “put” method which is also called TLM export would be in the consumer that reads the transaction created by producer, thus establishing a channel of communication while connect in class env in function connect().

Types of TLM ports/exports/imp:

Unidirectional Ports:

uvm_*_put_**

uvm_*_get_**

uvm_*_peek_**

uvm_*_get_peek_**

Bidirectional Ports:

uvm_*_master_**

uvm_*_slave_**

uvm_*_transport_**

Analysis Port

uvm_analysis_**

Note: Consider as following

** port/export/imp

* blocking/nonblocking/combined

TLM_FIFO:

A TLM FIFO is used for Transactional communication if both the producing component and the consuming component need to operate independently. In this case (as shown above), the producing component generates transactions and “puts” into FIFO, while the consuming component gets one transaction at a time from the FIFO and processes it.

uvm_analysis_port

Analysis ports/FIFOs are another transactional communication channel which are meant for a component to distribute (or broadcast) transaction to more than one component.

We can say like normal put_port/get_port: One to one connection it means one component puts the transaction and only one component get the transaction.

While analysis_port: One to many connection it means one component broadcast the transactions to the multiple components

Hierarchical Connections:

When there is a need for doing connect ports/exports of child class to parent class then it can be connected as shown in the below figure:

General Rules for TLM connections

The connect method of the child component port is always invoked with the child component export as the argument.

When connecting child ports to parent ports, the connect() method of the child port is called with the parent port as the argument.

When connecting child exports to parent exports, the connect() method of the parent export is called with the child export as the argument.

Â

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ NăngMong Muốn Có Thêm Cơ Hội Trong Công Việc

Â

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON