Difference in Normal Pci and Pci-Express -> 1. Bus topology

PCI uses a shared parallel bus architecture, in which PCI host and all devices share a common set of data/adress and control signals but in PCIe , it is based on point to point connection with separate serial link connecting to every device to the root complex.

2. Bandwidth

Because of bus topology in PCI, it is limited to one master at a time, in a single direction.

3. Performance

In older PCI, clocking scheme limits the bus to the lowest peripheral on the bus but in PCIe there is no such limitation because of point to point endpoints.

Inside of PCIe

The PCIe link between two devices can consist of anywhere from one to 32 lanes. PCIe is packet based protocol and for multi lane link, the packet data is striped across lanes. The lane count is automatically negotiated during link initialization. A single lane PCIe card can be inserted into a multi lane slot , during initialization , link will dynamically down-configure itself to use fewer lanes.

PCIe devices communicate via a logical connection called link. A link is point to point communication channel between twp PCIe ports allowing then to receive and send data . At physical layer, a link is composed of one or more lanes.

Lane

A Lane is composed of two differential signalling pair, one pair is to receive data and other one is to send data. Each lane is composed of four wires. So a 8-lane device with have 32 physical wires.

(adsbygoogle = window.adsbygoogle || []).push({}); History of PCIe ->

PCIe 1.0

In 2003 , PCI-SIG introduced PCIe 1.0 , with per lane data rate is 250 MB/s and transfer rate of 2.5 GT/s. It is expressed at GT/s (giga transfer per second) instead of bits per second , as it used 8b/10b encoding scheme which are overhead bits and does not provide additional throughput.

PCIe 1.1

In 2005, PCI-SIG introduced PCIe 1.1 , fully compatible with 1.0 with some clarification and improvements over PCIe 1.0

PCIe 2.0

In 2007 Jan, PCI-SIG announced the PCIe base 2.0 specification. It is compatible with PCIe 1.0 and having transfer rate of 5 GT/s.

PCIe 2.1

PCIe 2.1 supports a large proportion of the management, support and troubleshooting systems planned for full implementation in PCIe 3.0. However, the speed is the same as PCIe 2.0.

PCIe 3.0

PCIe Base Specification revision 3.0 was made available in Nov 2010. PCIe 3.0 having transfer rate of 8GT/s. PCIe 3.0 Specification include a number of optimizations for enhanced signalling and data integrity, including transmitter and receiver equalization , PLL improvement, clock data recovery and channel enhancements. It is compatible with PCIe1.0 and PCIe 2.0.

PCIe 3.1

PCIe 3.1 Specification was release in Nov 2014 , compatible with PCIe 3.0 , PCIe 2.0 , PCIe 1.0.

It has improvements in three areas , Power management , performance and functionality.

PCIe 4.0

Final Specification in expected to be released in 2017.

PCIe 1.0 -> 2.5 GT/s

PCIe 2.0 -> 5.0 GT/s

PCIe 3.0 -> 8.0 GT/s

PCIe 4.0 -> 16.0 GT/s

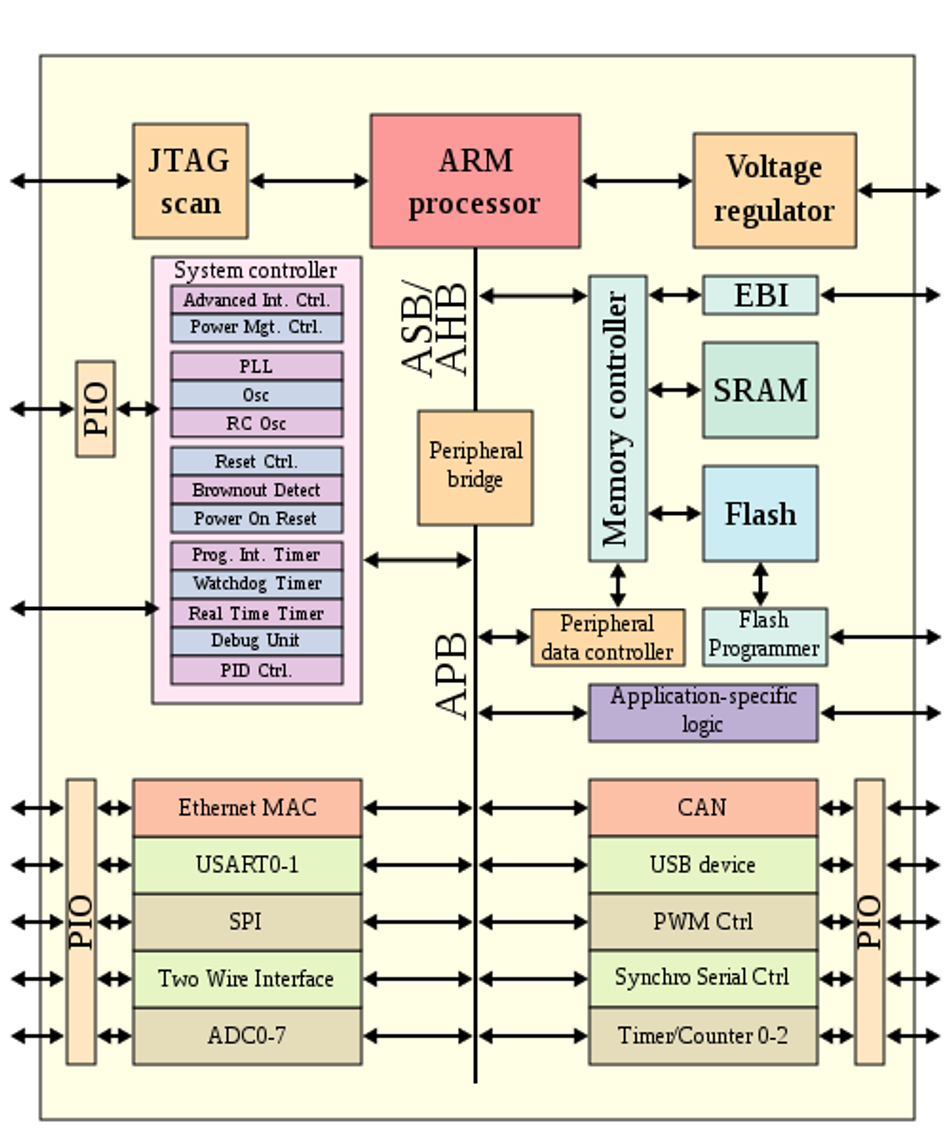

PCIe 1.0 / 2.0 /3.0 Architecture

PCIe 1.0/2.0/3.0

PCIe 1.0/2.0/3.0 architecture is divided in three layers.

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn