Băng thông đọc lớn và độ trễ truy cập nhỏ đã làm cho công nghệ NOR Flash được lựa chọn cho thực thi mã lệnh thời gian thực từ bộ nhớ không bay hơi. Các linh kiện Parallel NOR là sự lựa chọn cho nhiều ứng dụng, nhưng số chân của linh kiện bộ nhớ nối tiếp ngày càng trở nên hấp dẫn đối với nhiều hệ thống di động và nhúng.

Tính sẵn có của bộ nhớ NOR Flash mới được dựa trên giao tiếp ngoại vi với chế độ nối tiếp (SPI) cung cấp cho người phát triễn thực hiện Parallerl NOR trong khi làm giảm đáng kể số lượng chân của linh kiện.

Với sự phức tập gia tăng của các thiết bị di động ngày nay và các hệ thống nhúng, các nhà phát triễn phải giải quyết các nhiệm vụ ngày cách thách thức của các hệ thống con với truy suất tối ưu bộ nhớ mà làm tăng hiệu suất của hệ thống. Cụ thể, các hệ thống này thường có bộ nhớ chương trình kích thước MByte được lưu trữ trong bộ nhớ không bay hơi. Đối với hệ thống mà trong đó hiệu suất là cần thiết, thì mã chương trình có thể được truyền từ bộ nhớ không bay hơi đến RAM nhanh để tăng tốc thực thi. Đối với hệ thống mà kích thước thiết bị và giá cả là được quan tâm hàng đầu, thì mã chương trình có thể được thực thi trực tiếp từ bộ nhớ không bay hơi bằng cách sử dụng phương pháp biết trước như Execute-in-Place (XiP)

Với cách tiếp cận nào, thì hệ thống bộ nhớ có một tác động đáng kể đến toàn bọ hiệu suất hệ thống và kinh nghiệm người sử dụng. Nói chung, băng thông bus càng lớn, thì kinh nghiệm người sử dụng hệ thống càng tốt. Băng thông đọc cao và độ trễ nhỏ cho phép cách mã lệnh được sao chép hoặc nạp trước nhanh hơn. Một số yếu tố khác cũng quan trọng đối với người phát triễn để xem xét khi lựa chọn một công nghệ bộ nhớ không bay hơi.

Parallel NOR Flash

Linh kiện Parallel NOR Flash đã tồn tại gần 25 năm, và bus đã được phát triễn theo thời gian để cung cấp mức độ ngày càng tăng của hiệu suất. Các loại linh kiện NOR có sẵn tương thích với một hoặc nhiều hơn ba loại giao thức bus sau:

- Async Mode: Mỗi vận hành đọc 16 bit (2 byte) yêu cầu một mảng truy cập duy nhất cho tất cả mỗi vận hành đọc

- Page Mode: Một loạt chuỗi địa chỉ (thường là 32 byte) được độc từ mảng trong một lần truy cập đơn. Từ đích (2 byte) được đưa ra trong quá trình truy cập khởi tạo và sau đó truy cấp tiếp theo trong vùng 32 byte, một thời gian truy cập ngắn hơn "intra - page" là có thể được (ví dụ, khi chỉ thay đổi thứ tự các bit địa chỉ thấp). Bất kỳ truy cập bên ngoài phạm vi chuỗi địa chỉ trang 32 byte sẽ phải chịu thời gian khởi tạo truy cập lâu hơn "inter-page"

- Burst Mode: Giống như chế độ trang, chế độ đọc burst một chuỗi địa chỉ tiếp giáp nhau (thường là 32 byte) từ mảng trong lúc một truy cập khởi tạo đơn. Sau thời gian truy cập khởi tạo được yêu cầu đã trôi qua, dữ liệu được chạy ra ngoài một cách được định trước. Chế độ Burst đòi hỏi một vài chân mở rộng (thường là 3 chân) nhưng tỷ lệ mà tại đó dữ liệu có thể được chạy ra ngoài cung cấp một thông lượng cao hơn chế độ page hoặc chế độc async.

SPI-DDR NOR Flash

Số chân bus chịu đựng một ràng buộc thiết kế tới hạn đối với các ứng dụng di động và nhúng. Chân I/O là không miễn phí: mỗi chân I/O cộng thêm chi phí sản xuất và PCD layout cũng như thêm vào kích thước của linh kiện. Số pin đã trở thành một yếu tố quyết định khi lựa chọn giữa bộ nhớ NOR-based không bay hơi hay NAND-based.

Trong lịch sử, hệ thống sử dụng bộ nhớ NOR-based sử dụng một bus song song giữa các SoC máy chủ và một thiết bị bộ nhớ mở rộng. Các kiến trúc bus bộ nhớ song song cung cấp băng thông đọc cao và độ trễ thấp nhưng chúng trả giá cho chi phí sống cân cao hơn so với kiến trúc bus nối tiếp. Kiến trúc bus nối tiếp có số chân giảm xuống nhưng với chi phí băng thông thấp hơn và độ trễ lơn hơn. Thách thức cho người phát triễn là có được băng thông cao mà số lượng chân ít lại.

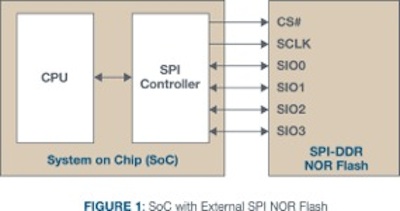

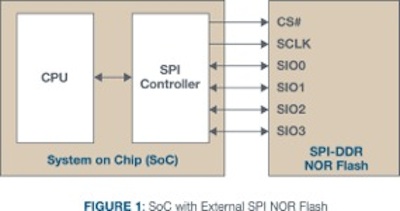

Bây giờ các nhà phát triễn có sự tùy chọn việc sử dụng bộ nhớ NOR Flash dựa trên giao tiếp ngoại vi chế độ nối tiếp (SPI) để đáp ứng nhu cầu của các ứng dụng di động và nhúng. SPI là một giao diện linh hoạt, cân bằng số lượng chân và băng thông để tối đa hóa hiệu suất tổng thể của hệ thống với chi phí thấp hơn. SPI là một tiêu chuẩn được thành lập để phục vụ ngành công nghiệp điện tử trong hơn 25 năm. Đã có một loạt các chipset và các thiết bị ngoại vi hỗ trợ SPI. Các tiêu chuẩn SPI cũng đã rất ổn định trong những năm qua. Trong khi điện áp hoạt động đã giảm và tốc độ xung nhịp tăng lên để cải thiện băng thông, lệnh giao thức bên trong vẫn được giữ nguyên.

SPI tiếp tục phát triễn để đáp ứng nhu cầu thị trường thay đổi. Để cung cấp thông lượng và hỗ trợ chức năng (MIO) đa ngõ vào/ra, giao diện đã được mở rộng để chứa cấu hình 2-bit IO và 4-bit IO. Để cải thiện thông lượng của thiết bị hơn nữa gần đây đã được giới thiệu mà sử dụng giao thức nhân đôi tốc độ dữ liệu (DDR). Sự kết hợp của tất cả những cải tiến này - tầng số cao hơn, 4-bit I/O và bây giờ DDR - đã có kết quả SPI-DDR NOR. SPI-DDR ban đầu sử dụng điện áp vận hành 3V mà cho phép tần số vận hành của bus là 66MHz đến 100MHz. Sự tiến bộ trong tương lại gồm chức năng SPI-DDR với điện áp 1.8V mà được mong đợi để đạt được tầng số vận hành từ 100MHz và 133MHz. Với băng thông được nâng cao, độ trễ truy cập nhỏ, và đóng gói giao tiếp bus 6 chân, SPI-DDR NOR cung cấp một thay thế hấp dẫn ch thiết bị di động và nhúng với chi phí thấp có lịch sử sử dụng Parallel NOR do hiệu suất cao hơn.