Mục tiêu đầu tiên là thiết kế ALU 32-bit có thực hiện phép toán AND, OR và cộng. Đầu tiên để hiểu rõ được những điều dưới đây bạn cần hiểu ALU là gì ?

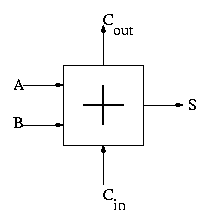

Ta sẽ bắt đầu với bộ cộng đầy đủ (full adder) như hình dưới đây:

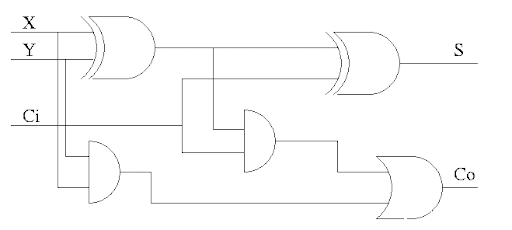

Sơ đồ mạch thực hiện khối full adder là như sau:

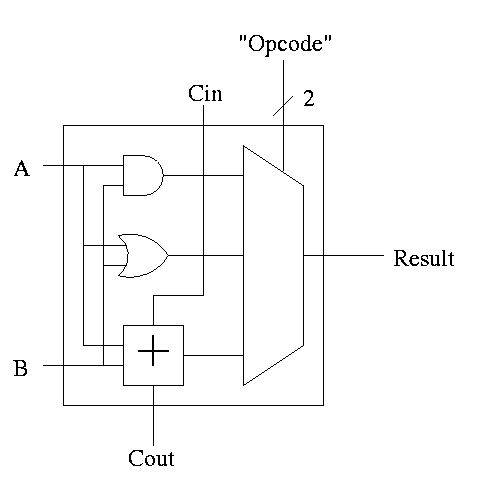

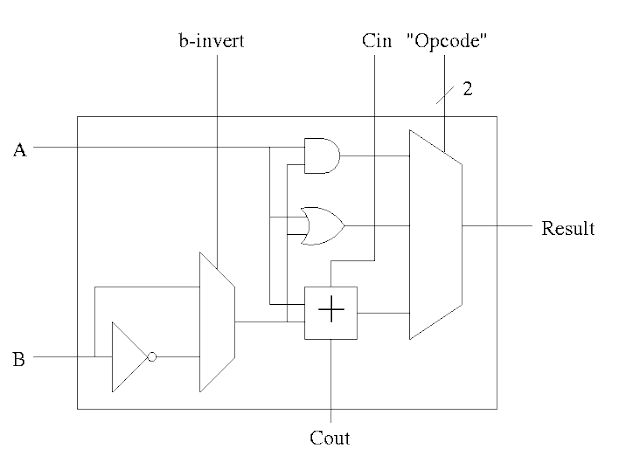

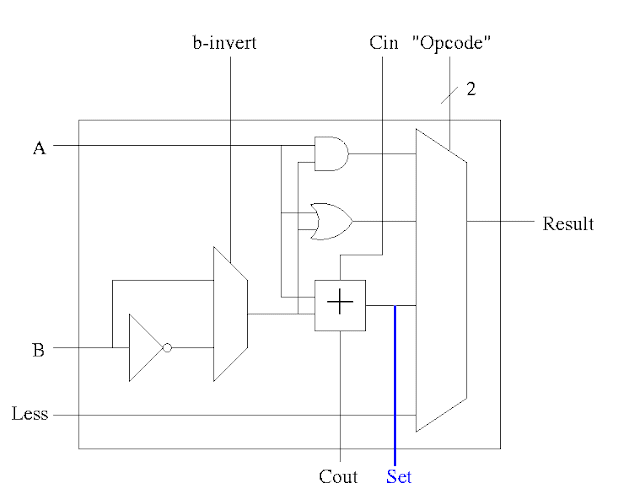

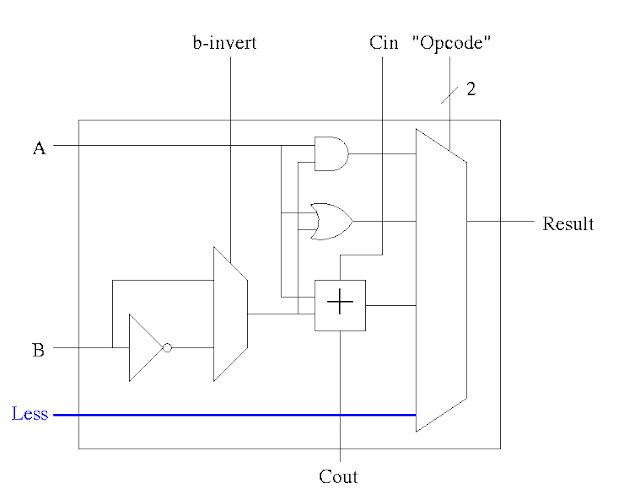

Để có thể lựa chọn kết quả cho đúng các phép toán, ta đưa ngõ ra các mạch đến MUX và tín hiệu chọn lựa được trích từ mã lệnh của lệnh hiện tại (ADD, AND, OR). Ta được khối ALU dùng tính cho 1 bit.

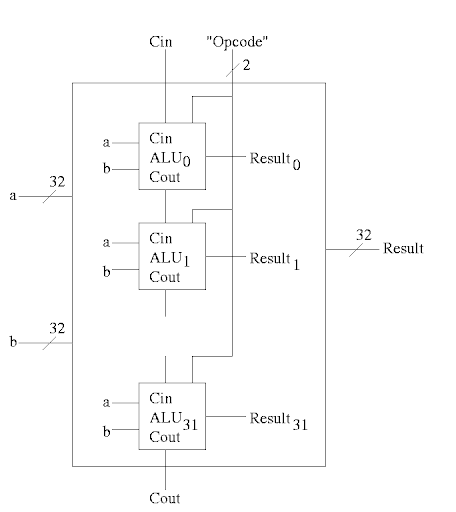

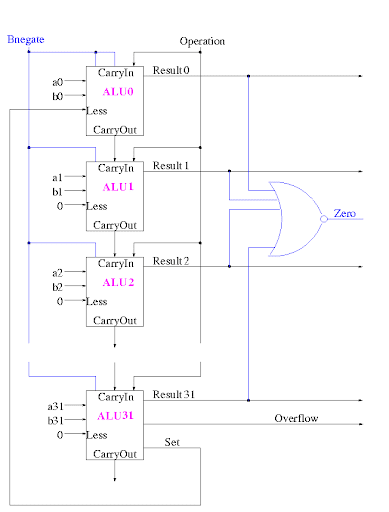

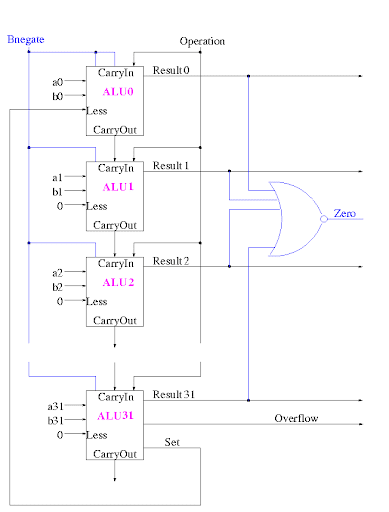

Việc tạo ra khối ALU 32-bit thì đơn giản là ghép 32 khối ALU 1-bit lại thôi.

Như vậy là hoàn thành mục tiêu đầu tiên.

Về phần ý nghĩa của các tên tín hiệu thì như sau:

A: toán hạng 1

B: toán hạng 2

Cin: giá trị của cờ nhớ vào (Carry In)

Cout: giá trị của cờ nhớ ra (Carry Out)

Result: kết quả sau khi tính toán

ALU hỗ trợ phép trừ

Ý tưởng để giải quyết là thực hiện cộng với bù 2.

A - B = A + (bù 2 của B ) = A + (bù B + 1)

Ta có được bù B bằng cách cho B qua cổng NOT

Giá trị +1 thêm vào nhận từ CarryIn ngõ vào

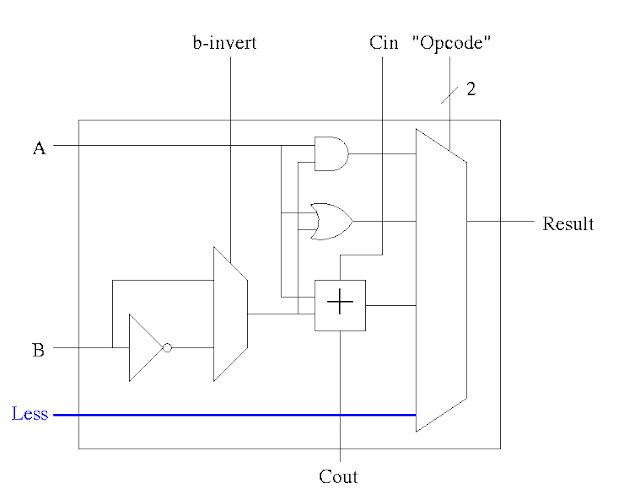

1-bit ALU hỗ trợ các phép toán ADD, SUB, AND, OR

Để thực hiện phép trừ thì gán tín hiệu Binvert và Cin giá trị 1.

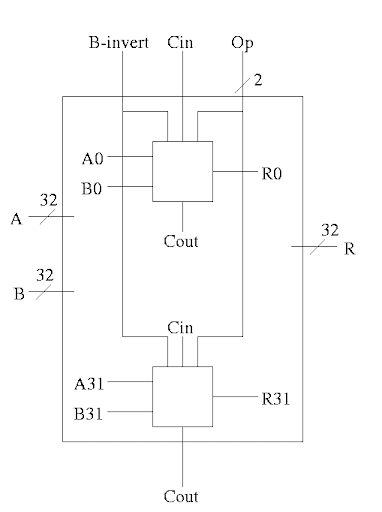

Thực hiện ALU 32-bit thì tương tự ghép 32 khối ALU 1-bit lại với nhau.

• Để trừ gán B-invert và Cin giá trị 1.

• Để thực hiện cộng thì cho B-invert và Cin giá trị 0.

• Để AND và OR thì gán B-invert giá trị 0 còn Cin thì không cần quan tâm

Như vậy ta đã hoàn tất ALU có hỗ trợ ADD, SUB, AND và OR

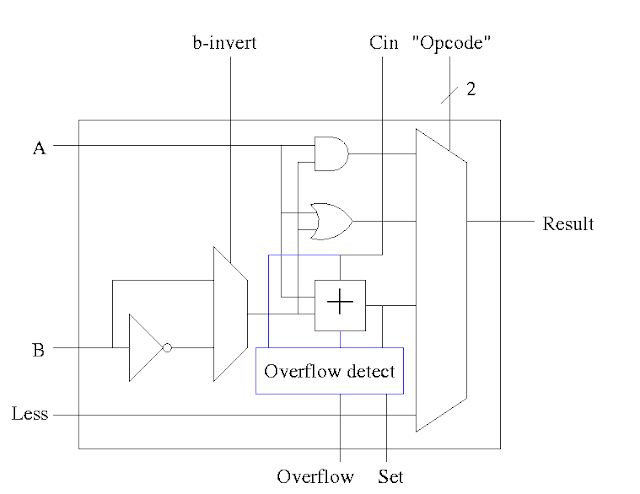

Yêu cầu: hỗ trợ trả về giá trị các cờ Zero, Overflow và So sánh bé hơn (set less than) như hình bên dưới.

[img]http://lh4.ggpht.com/_lbL2GqfpYxw/S-LKnYy4WuI/AAAAAAAAAI. So sánh bé hơn (slt: set less than)

o Kết quả là 1 nếu a < b

o Kết quả là 0 nếu a >= b

o Ta cần gán giá trị của bit thấp nhất LSB (least significant bit) của kết quả bằng bit dấu của phép trừ, và gán các bit còn lại giá trị 0.

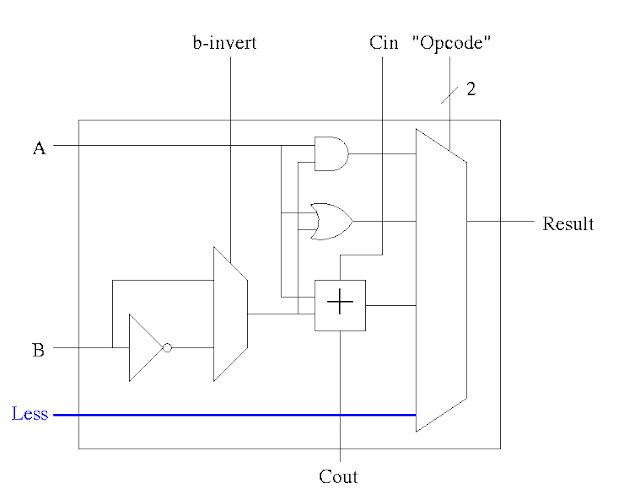

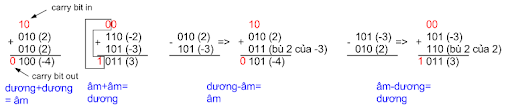

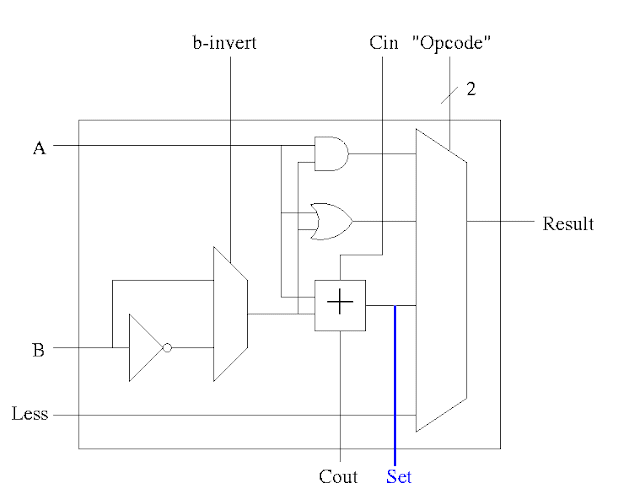

Ý tưởng 1: Thêm 1 ngõ vào cho MUX gọi là LESS. Ngõ vào này được chọn khi mã lệnh là slt. Đối với tất cả các bit ngoại trừ bit LSB, ngõ vào LESS có giá trị là 0. Chúng ta phải nghĩ cách để ngõ vào LESS gán bit LSB có giá trị là 1 khi a

Ý tưởng 2: Lấy kết quả của bộ cộng trước MUX của bit MSB, gọi nó là SET, và gán cho tín hiệu LESS của bit LSB trong ý tưởng 1. Ngõ vào LESS của các bit khác gán giá trị 0 cho nó. Giá trị của SET chính là bit dấu sau khi thực hiện phép trừ.

1. Câu hỏi đặt ra ở đây là: cách thực hiện này có đúng ko?

2. Câu trả lời: Nó sai!

3. Ví dụ với số 3-bit: thử so sánh hai số -3 và +2. Kết quả đúng phải là -3 - +2 là -5. Bit dấu âm của -5 chỉ ra rằng -3 < +2 là đúng. Nhưng phép trừ 3-bit của -3 - +2 sẽ cho kết quả là +3 ! Vì vậy việc so sánh sẽ cho kết quả sai. Trong trường hợp này cờ overflow sẽ tích cho bit kết quả tính toán bị sai ngoại trừ trường hợp trừ với số không dấu.

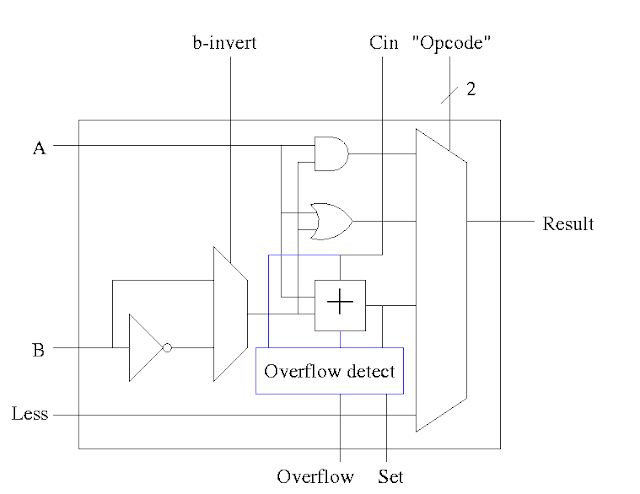

4. Cách giải quyết: Khi tín hiệu Overflow tích cực thì ta sẽ lấy bù gía trị của tín hiệu SET sẽ cho ra kết quả đúng.

II. Cờ báo tràn (Overflow flag)

Trong phần này ta sẽ nâng cấp để ALU có thể trả về cờ báo tràn. Ta có 4 trường hợp xảy ra tràn:

Do đó cách đơn giản để phát hiện Overflow là XOR bit nhớ vào bit MSB của ALU và bit nhớ ngõ ra của nó.

III. Cờ báo bằng 0 (Zero flag)

Cách giải quyết: cờ Zero tích cực khi tất cả các bit kết quả = 0, vì lấy ta sẽ thực hiện NOR tất cả các bit kết quả với nhau để phát hiện Zero.

Ta có thể quan sát thấy rằng giá trị của Cin và Binvert thì luôn giống nhau. Do đó ta dùng cho 1 tín hiệu cho cả 2 ngõ vào và gọi nó là Bnegate.

Cuối cùng ta có được kết quả như sau:

Đến đây ta đã thiết kế được ALU hỗ trợ các phép toán AND, OR, ADD, SUB, SLT và có cờ báo trạng thái kết quả ngõ ra Zero, Overflow

[img]http://lh4.ggpht.com/_lbL2GqfpYxw/S-LKnYy4WuI/AAAAAAAAAI. So sánh bé hơn (slt: set less than)

o Kết quả là 1 nếu a < b

o Kết quả là 0 nếu a >= b

o Ta cần gán giá trị của bit thấp nhất LSB (least significant bit) của kết quả bằng bit dấu của phép trừ, và gán các bit còn lại giá trị 0.

Ý tưởng 1: Thêm 1 ngõ vào cho MUX gọi là LESS. Ngõ vào này được chọn khi mã lệnh là slt. Đối với tất cả các bit ngoại trừ bit LSB, ngõ vào LESS có giá trị là 0. Chúng ta phải nghĩ cách để ngõ vào LESS gán bit LSB có giá trị là 1 khi a

Ý tưởng 2: Lấy kết quả của bộ cộng trước MUX của bit MSB, gọi nó là SET, và gán cho tín hiệu LESS của bit LSB trong ý tưởng 1. Ngõ vào LESS của các bit khác gán giá trị 0 cho nó. Giá trị của SET chính là bit dấu sau khi thực hiện phép trừ.

1. Câu hỏi đặt ra ở đây là: cách thực hiện này có đúng ko?

2. Câu trả lời: Nó sai!

3. Ví dụ với số 3-bit: thử so sánh hai số -3 và +2. Kết quả đúng phải là -3 - +2 là -5. Bit dấu âm của -5 chỉ ra rằng -3 < +2 là đúng. Nhưng phép trừ 3-bit của -3 - +2 sẽ cho kết quả là +3 ! Vì vậy việc so sánh sẽ cho kết quả sai. Trong trường hợp này cờ overflow sẽ tích cho bit kết quả tính toán bị sai ngoại trừ trường hợp trừ với số không dấu.

4. Cách giải quyết: Khi tín hiệu Overflow tích cực thì ta sẽ lấy bù gía trị của tín hiệu SET sẽ cho ra kết quả đúng.

II. Cờ báo tràn (Overflow flag)

Trong phần này ta sẽ nâng cấp để ALU có thể trả về cờ báo tràn. Ta có 4 trường hợp xảy ra tràn:

Do đó cách đơn giản để phát hiện Overflow là XOR bit nhớ vào bit MSB của ALU và bit nhớ ngõ ra của nó.

III. Cờ báo bằng 0 (Zero flag)

Cách giải quyết: cờ Zero tích cực khi tất cả các bit kết quả = 0, vì lấy ta sẽ thực hiện NOR tất cả các bit kết quả với nhau để phát hiện Zero.

Ta có thể quan sát thấy rằng giá trị của Cin và Binvert thì luôn giống nhau. Do đó ta dùng cho 1 tín hiệu cho cả 2 ngõ vào và gọi nó là Bnegate.

Cuối cùng ta có được kết quả như sau:

Đến đây ta đã thiết kế được ALU hỗ trợ các phép toán AND, OR, ADD, SUB, SLT và có cờ báo trạng thái kết quả ngõ ra Zero, Overflow

êu cầu: ALU hỗ trợ thêm các lệnh dịch trái và dịch phải

Ý tưởng thực hiện như sau:

Dùng 1 MUX để chọn lấy kết quả từ các phép toán ADD, SUB, AND, OR, SLT hoặc từ bộ dịch.

Chi tiết về thiết kế bộ dịch như hình bên dưới. Các bộ dịch bên dưới đều hỗ trợ dịch trái hoặc phải với số bit tương ứng.

VD: shift_amount[4:0] = 5’b10101 (21 decimal)

Giá trị A qua các tầng như sau:

* Tầng 1 sẽ dịch được 1 bit

* Tầng 2 sẽ giữ nguyên nghĩa là dịch được 1 bit

* Tầng 3 sẽ dịch thêm 4 bit nữa là dịch được 5 bit

* Tầng 4 sẽ giữ nguyên nghĩa là dịch tất cả được 5 bit

* Tầng 5 sẽ dịch thêm 16 bit nữa là dịch được 21 bit tất cả, đúng như số lượng cần dịch.

Về vấn đề bộ dịch trái và phải các bạn có thể dùng MUX và chọn các bit ngõ vào để thực hiện việc dịch. Nó sẽ có thêm tín hiệu chọn là left_right (cái này không cần nêu quá chi tiết).

Các bạn có thể thực hiện việc dịch với 1 MUX duy nhất và ngõ vào chọn MUX chính là các bit left_right và shift_amount[4:0]. Nhưng mạch thiết kế như vậy sẽ rất tốn phần cứng trong trường hợp là 32-bit dữ liệu. Vì vậy mạch mà mình giới thiệu ở trên đã tiết kiệm được số lượng lớn tài nguyên. Có một hạn chế là: qua 5 tầng thì tốc độ của mạch này sẽ chậm hơn một chút so với mạch lấy shift 1 lần duy nhất.

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)