Compile Commands

# Point to your systemC home SYSTEMC_HOME = /appl/systemc

INC_OPT = -I. -I$(VCS_HOME)/include \ -I$(SYSTEMC_HOME)/include COMP_OPT = -c LIB_OPT = $(SYSTEMC_HOME)/lib-linux/libsystemc.a CPP_FILE = memory_txGen.cpp memory_tb.cpp PLI_C_FILE = memory_pli.c V_FILE = memory.v PLI_O_FILE = memory_txGen.o memory_pli.o memory_tb.o VCS_OPT = -CFLAGS -lstdc++ $(LIB_OPT) \ -lscv -L$(SYSTEMC_HOME)/lib-linux -lsystemc # Invoke VCS pli: c cpp vcs -P memory_pli.tab $(PLI_O_FILE) \ memory.v $(VCS_OPT) -R # Compile CPP file cpp : $(CPP_FILE) gcc $(INC_OPT) $(COMP_OPT) $(CPP_FILE) # Compile the PLI C file c : $(PLI_C_FILE) gcc $(INC_OPT) $(COMP_OPT) $(PLI_C_FILE) clean: rm -rf *.o simv csrc simv.daidir vcs.key *.vpd *.vcd Simulation Output

1 Note: VCD trace timescale unit is set by user to 1e-9 sec.

2 @0 s Started SystemC Schedular

3 @2 ns Starting the memory write/read test

4 @2 ns Writing address : 34

5 @6 ns Reading address : 34

6 @8 ns Match : Write data : 1810566829 Read data : 1810566829

7 @10 ns Writing address : 21

8 @14 ns Reading address : 21

9 @16 ns Match : Write data : 733289676 Read data : 733289676

10 @18 ns Writing address : 248

11 @22 ns Reading address : 248

12 @24 ns Match : Write data : 3412074928 Read data : 3412074928

13 @26 ns Writing address : 53

14 @30 ns Reading address : 53

15 @32 ns Match : Write data : 3173768033 Read data : 3173768033

16 @34 ns Writing address : 15

17 @38 ns Reading address : 15

18 @40 ns Match : Write data : 1734425763 Read data : 1734425763

19 @42 ns Writing address : 59

20 @46 ns Reading address : 59

21 @48 ns Match : Write data : 4221480844 Read data : 4221480844

22 @50 ns Writing address : 137

23 @54 ns Reading address : 137

24 @56 ns Match : Write data : 1183138391 Read data : 1183138391

25 @58 ns Writing address : 139

26 @62 ns Reading address : 139

27 @64 ns Match : Write data : 3811330364 Read data : 3811330364

28 @66 ns Writing address : 90

29 @70 ns Reading address : 90

30 @72 ns Match : Write data : 2171416917 Read data : 2171416917

31 @74 ns Writing address : 231

32 @78 ns Reading address : 231

33 @80 ns Match : Write data : 3785749466 Read data : 3785749466

34 =======================================

35 SIMULATION PASSED

36 =======================================

37 @83 ns Stopping SystemC Schedular

38 SystemC: simulation stopped by user.

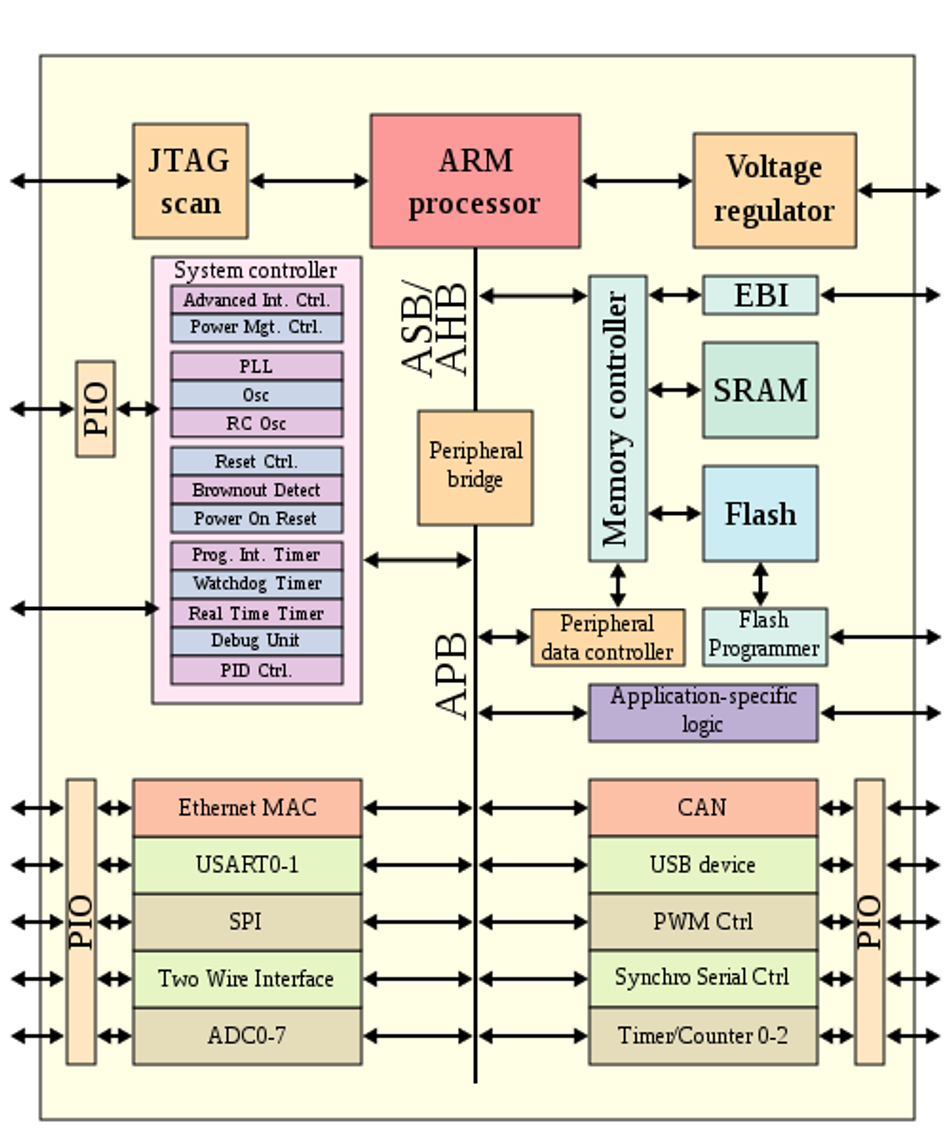

VPI Interface

For the SystemC to work with Verilog PLI 2.0 or VPI following sequence of operations need to be performed.

- Callback :Add callback on all the output signals of HDL, clock and reset in such a way that, when ever they change. PLI code gets control.

- Sample : Sample all the inputs to SystemC or outputs of HDL.

- sc_start(time) : sc_start method of systemC with parameter time. Where time is difference between last call time and current time.

- Drive : Drive all the outputs of SystemC or inputs to HDL.

Other then this, we need to perform few other tasks listed below.

- Initilize the SystemC Model, when PLI task is executed for first time.

- Type conversion between SystemC and PLI

- Terminate SystemC model, Like closing VCD file, when $finish is encountered in HDL.

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn