Chia tần số trên FPGA

Monday, 27 July 2015 20:05

![[IMG]](https://lh6.googleusercontent.com/G04lXoDgcsFO5g6n72__txVtCvkiHlllS4rRN9yxu9c=w960-h398-no) Dao động và tần số Dao động và tần số

- Một thành phần rất quan trọng của bất kỳ board mạch FPGA là bộ dao động crystal. Các dao động phát ra một dãy 0,1 tại một thời gian nhất định dựa trên tần số của nó.

Read more...

|

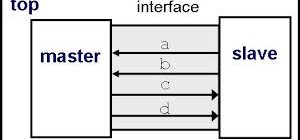

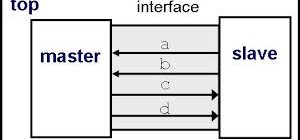

Tìm hiểu Interface trong SystemVerilog

Saturday, 25 July 2015 17:07

Một trong những tính năng hay nhất mà SystemVerilog hỗ trợ là từ khóa interface. Các kĩ sư thiết kế không còn phải tốn thời gian để lặp đi lặp lại công việc nối dây (wire connectivity) giữa module với module, hay module với testbench. Một trong những tính năng hay nhất mà SystemVerilog hỗ trợ là từ khóa interface. Các kĩ sư thiết kế không còn phải tốn thời gian để lặp đi lặp lại công việc nối dây (wire connectivity) giữa module với module, hay module với testbench.

Read more...

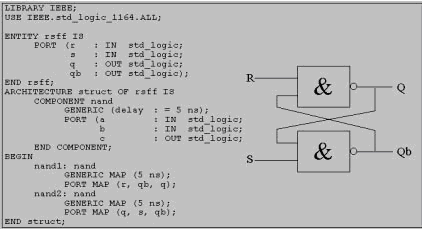

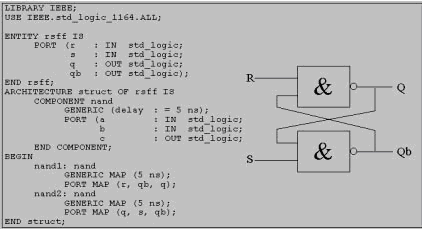

Ngôn ngữ mô tả phần cứng VHDL

Saturday, 25 July 2015 11:07

1. Giới thiệu về VHDL 1. Giới thiệu về VHDL

VHDL là viết tắt của cụm từ Very High Speed Intergrated Circuit Hardware Description Language - ngôn ngữ mô phỏng phần cứng cho các mạch tích hợp tốc độ rất cao.

Last Updated ( Wednesday, 18 November 2015 14:57 )

Read more...

Coverage trong thiết kế Verilog (kiểm tra mức độ bao phủ trong quá trình test)

Friday, 24 July 2015 19:14

Nguyễn Thị Loan

1. Giới thiệu về Coverage trong thiết kế RTL 1. Giới thiệu về Coverage trong thiết kế RTL Coverage (độ bao phủ) là phương pháp thống kê trong quá trình kiểm tra thiết kế (verification) để xác định được chất lượng của quá trình kiểm tra. Phương pháp thu thập thông tin này thường được làm một cách tự động bởi các công cụ mô phỏng.

Last Updated ( Tuesday, 18 June 2019 20:01 )

Read more...

Tìm hiểu về SystemVerilog Assertion

Thursday, 23 July 2015 16:27

Nguyễn Thị Loan

Verilog assertion có nhiều điểm hạn chế do bản thân ngôn ngữ không hỗ trợ trực tiếp việc viết Assertion mà phải thông qua các thư viện OVL hoặc PSL. Thêm vào đó, assertion trong Verilog phải được viết sao cho transparent với các công cụ thiết kế (không được tổng hợp). Verilog assertion có nhiều điểm hạn chế do bản thân ngôn ngữ không hỗ trợ trực tiếp việc viết Assertion mà phải thông qua các thư viện OVL hoặc PSL. Thêm vào đó, assertion trong Verilog phải được viết sao cho transparent với các công cụ thiết kế (không được tổng hợp).

Read more...

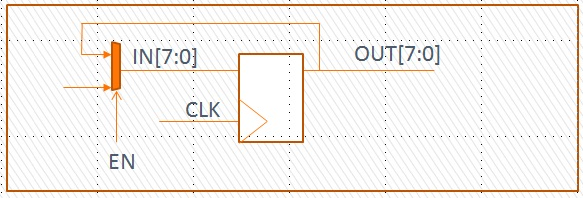

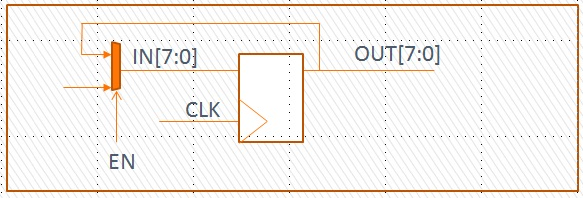

Kĩ thuật Gating clock trong Low Power Design

Thursday, 23 July 2015 13:45

Nguyễn Thị Loan

Bài giới thiệu về clock gating. Một trong những kĩ thuật được áp dụng nhằm giảm mức tiêu hao năng lượng của mạch. Bài giới thiệu về clock gating. Một trong những kĩ thuật được áp dụng nhằm giảm mức tiêu hao năng lượng của mạch.

Last Updated ( Thursday, 23 July 2015 14:04 )

Read more...

Kiến trúc clock trong System On Chip

Wednesday, 22 July 2015 16:45

Tìm hiều về kiến trúc clock của hệ thống System On Chip (SoC) Tìm hiều về kiến trúc clock của hệ thống System On Chip (SoC)

Một trong những kiến trúc clock thông dụng trong một hệ thống SoC được mô tả như hình dưới đây.

Read more...

Đồng hồ bấm giờ trên FPGA dùng verilog

Wednesday, 22 July 2015 14:32

Thời gian tối đa của đồng hồ này là 10p. Đồng hồ này gồm 4 chữ số để đếm từ 0:00:0 tới 9:59:9. Chữ số đầu tiên bên phải sẽ dùng một bộ đếm tăng lên 0,1s. Khi chữ số đó đạt đến 9 thì hai chữ số ở giữa sẽ tăng lên 1 đơn vị và chúng ta có bộ đếm thứ 2. Và khi 2 số ở giữa tăng đến 59 thì số đầu tiên bên trái sẽ tăng một đơn vị.Đồng hồ này hiển thị theo dạng M:SS:D. Thời gian tối đa của đồng hồ này là 10p. Đồng hồ này gồm 4 chữ số để đếm từ 0:00:0 tới 9:59:9. Chữ số đầu tiên bên phải sẽ dùng một bộ đếm tăng lên 0,1s. Khi chữ số đó đạt đến 9 thì hai chữ số ở giữa sẽ tăng lên 1 đơn vị và chúng ta có bộ đếm thứ 2. Và khi 2 số ở giữa tăng đến 59 thì số đầu tiên bên trái sẽ tăng một đơn vị.Đồng hồ này hiển thị theo dạng M:SS:D.

Read more...

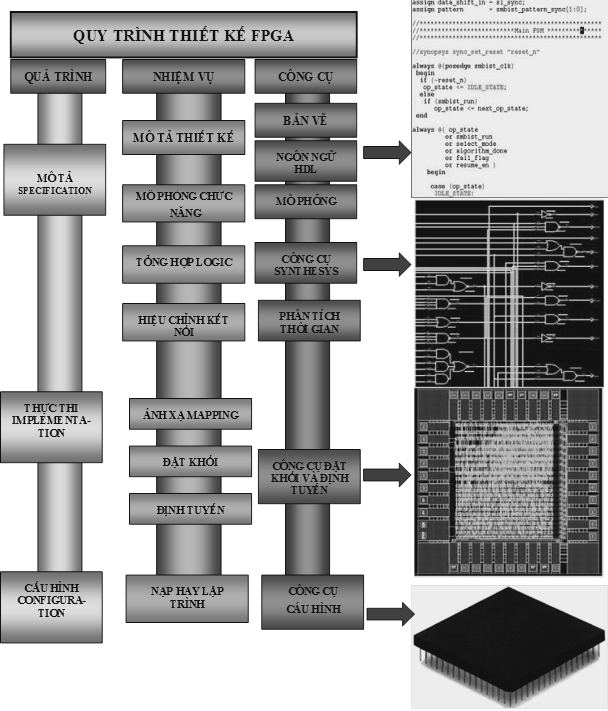

Quy trình thiết kế FPGA tổng quát.

Wednesday, 22 July 2015 13:45

administrator

Mô tả ban đầu về thiết kế. (Specification)- Khi xây dựng một chip khả trình (FPGA) với ý nghĩa dành cho một ứng dụng riêng biệt. Chính vì xuất phát từ mỗi ứng dụng trong thực tiễn cuộc sống, ta sẽ phải đặt ra yêu cầu thiết kế IC thực hiện tối ưu nhất những ứng dụng đó.

Last Updated ( Wednesday, 26 September 2018 19:34 )

Read more...

Tìm hiểu về Lint check trong thiết kế Verilog

Monday, 20 July 2015 15:17

Tìm hiểu về Lint check trong thiết kế Verilog HDL (RTL Rule Check) Tìm hiểu về Lint check trong thiết kế Verilog HDL (RTL Rule Check)

Trong thiết kế Verilog HDL, hàng loạt các quy tắc thiết kế được đưa ra nhằm đảm bảo việc các kĩ sư thiết kế sẽ tuân thủ các nguyên tắc về cấu trúc code, filename, comment, sự phân lớp khi coding, các quy tắc khi thiết kế đồng bộ, bất đồng bộ …

Last Updated ( Monday, 20 July 2015 19:13 )

Read more...

Sử dụng hiệu quả tính năng Windows System Restore

Saturday, 18 July 2015 08:04

Máy tính của bạn ắt hẳn từng vài lần bị treo rồi dẫn đến tình trạng không thể khởi chạy ổn định ở lần sử dụng tiếp theo. Khi đó, một cột mốc khôi phục hệ thống (restore point) sẽ phát huy tác dụng.

Read more...

Đọc thông số PIC, lựa chọn PIC và sản xuất với PIC

Friday, 17 July 2015 20:08

Để lựa chọn một dòng sản phẩm PIC 8-bit bất kỳ cho dự án của các bạn, công việc của các bạn cần làm: Để lựa chọn một dòng sản phẩm PIC 8-bit bất kỳ cho dự án của các bạn, công việc của các bạn cần làm:

Thiết kế >>> Thử nghiệm >>> Sản xuất thử >>> Sản xuất

Read more...

Thiết kế verilog Verilog - Ram một port ĐỌC/GHI đồng bộ

Friday, 17 July 2015 16:57

Please refer to dual port RAM. Please see code of this in this article. Table 1. General Benefits / Drawbacks of Single Port Asynchronous Synchronous Benefits

Tìm hiểu về ngắt trong MSP430

Friday, 17 July 2015 15:08

![[IMG]](https://lh5.googleusercontent.com/-B34vvhZrRHI/VR9fOeh7AaI/AAAAAAAACF4/Cf5_hKjUGxY/w890-h860-no/msp43023.png) 1,Khái niệm:- Interrupt (ngắt): Là một sự kiện gây bởi phần cứng (mặc dù được cài đặt bằng phần mềm) và thường cần được xử lý ngay lập tức.Khi phát hiện ngắt, chương trình chính tạm dừng để thực hiện 1 chương ngắt. Khi thực hiện xong trở về chương trình hiện tại. 1,Khái niệm:- Interrupt (ngắt): Là một sự kiện gây bởi phần cứng (mặc dù được cài đặt bằng phần mềm) và thường cần được xử lý ngay lập tức.Khi phát hiện ngắt, chương trình chính tạm dừng để thực hiện 1 chương ngắt. Khi thực hiện xong trở về chương trình hiện tại.

Read more...

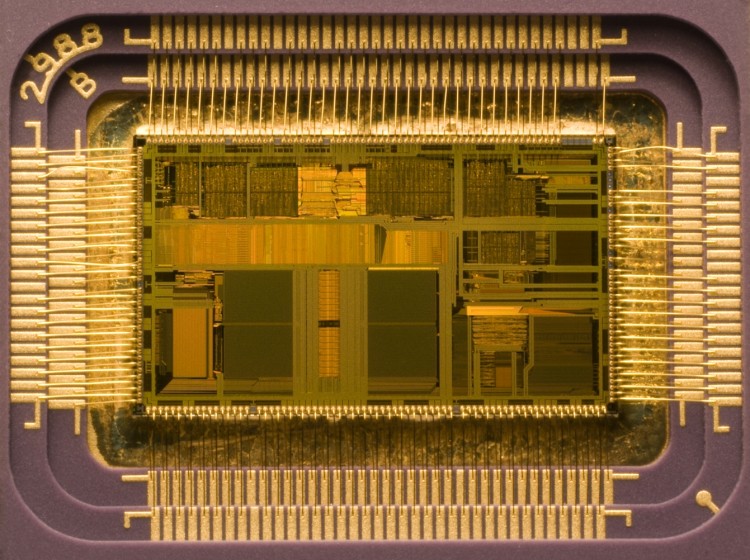

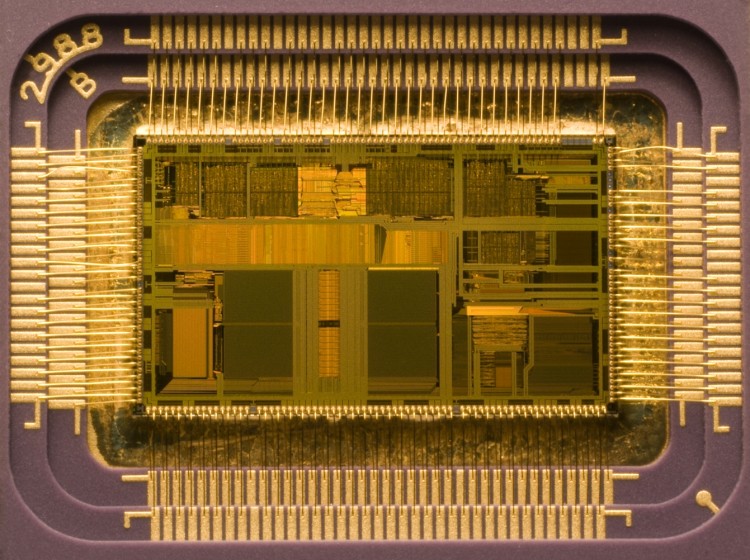

Lịch sử mạch bán dẫn IC

Wednesday, 15 July 2015 13:56

Nguyễn Thị Loan

Sơ lược về IC Sơ lược về IC

Vi mạch tích hợp, hay vi mạch, hay mạch tích hợp (integrated circuit, gọi tắt IC, còn gọi là chiptheo thuật ngữ tiếng Anh) là các mạch điện chứa các linh kiện bán dẫn (như transistor) và linh kiện điện tử thụ động (như điện trở) được kết nối với nhau, kích thước cỡ micrômét (hoặc nhỏ hơn) chế tạo bởi công nghệ silicon cho lĩnh vực điện tử học.

Last Updated ( Wednesday, 15 July 2015 14:24 )

Read more...

Tìm hiểu chi tiết về mạch khuếch đại thuật toán

Tuesday, 14 July 2015 20:28

Đây là một vi mạch tương tự. Mạch khuếch đại thuật toán (Op-Amps) có một ứng dụng rất rộng rãi trong kỹ thuật điện tử hiện đại. Đây là một vi mạch tương tự. Mạch khuếch đại thuật toán (Op-Amps) có một ứng dụng rất rộng rãi trong kỹ thuật điện tử hiện đại.

Last Updated ( Tuesday, 14 July 2015 20:53 )

Read more...

|

|

|

|

|

|

|

Page 105 of 118 |

Dao động và tần số

Một trong những tính năng hay nhất mà SystemVerilog hỗ trợ là từ khóa interface. Các kĩ sư thiết kế không còn phải tốn thời gian để lặp đi lặp lại công việc nối dây (wire connectivity) giữa module với module, hay module với testbench.

Một trong những tính năng hay nhất mà SystemVerilog hỗ trợ là từ khóa interface. Các kĩ sư thiết kế không còn phải tốn thời gian để lặp đi lặp lại công việc nối dây (wire connectivity) giữa module với module, hay module với testbench.

1. Giới thiệu về Coverage trong thiết kế RTL

1. Giới thiệu về Coverage trong thiết kế RTL Verilog

Verilog  Bài giới thiệu về

Bài giới thiệu về  Tìm hiều về

Tìm hiều về Thời gian tối đa của đồng hồ này là 10p. Đồng hồ này gồm 4 chữ số để đếm từ 0:00:0 tới 9:59:9. Chữ số đầu tiên bên phải sẽ dùng một bộ đếm tăng lên 0,1s. Khi chữ số đó đạt đến 9 thì hai chữ số ở giữa sẽ tăng lên 1 đơn vị và chúng ta có bộ đếm thứ 2. Và khi 2 số ở giữa tăng đến 59 thì số đầu tiên bên trái sẽ tăng một đơn vị.Đồng hồ này hiển thị theo dạng M:SS:D.

Thời gian tối đa của đồng hồ này là 10p. Đồng hồ này gồm 4 chữ số để đếm từ 0:00:0 tới 9:59:9. Chữ số đầu tiên bên phải sẽ dùng một bộ đếm tăng lên 0,1s. Khi chữ số đó đạt đến 9 thì hai chữ số ở giữa sẽ tăng lên 1 đơn vị và chúng ta có bộ đếm thứ 2. Và khi 2 số ở giữa tăng đến 59 thì số đầu tiên bên trái sẽ tăng một đơn vị.Đồng hồ này hiển thị theo dạng M:SS:D.

Để lựa chọn một dòng sản phẩm PIC 8-bit bất kỳ cho dự án của các bạn, công việc của các bạn cần làm:

Để lựa chọn một dòng sản phẩm PIC 8-bit bất kỳ cho dự án của các bạn, công việc của các bạn cần làm: Please refer to dual port RAM. Please see code of this in this article.

Please refer to dual port RAM. Please see code of this in this article.![[IMG]](https://lh5.googleusercontent.com/-B34vvhZrRHI/VR9fOeh7AaI/AAAAAAAACF4/Cf5_hKjUGxY/w890-h860-no/msp43023.png) 1,Khái niệm:

1,Khái niệm: Sơ lược về IC

Sơ lược về IC Đây là một vi mạch tương tự. Mạch khuếch đại thuật toán (Op-Amps) có một ứng dụng rất rộng rãi trong kỹ thuật điện tử hiện đại.

Đây là một vi mạch tương tự. Mạch khuếch đại thuật toán (Op-Amps) có một ứng dụng rất rộng rãi trong kỹ thuật điện tử hiện đại.