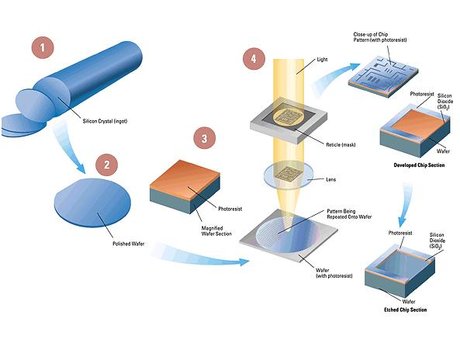

Khái quát quy trình sản xuất một Chip thông dụng

Tuesday, 14 July 2015 14:16

Các con Chip hiện nay đang tồn tại ở trong hầu hết các vật dụng điện tử, nhận thấy vai trò đóng góp to lớn của Chip do đó trên thế giới ngành công nghiệp để sản xuất ra những con chip hay những vi mạch tich hợp này hiện đang là một trong những lĩnh vực mới mẻ và hứa hẹn nhiều tiềm năng.

Read more...

|

Tìm hiểu về hiện tượng metastable

Monday, 13 July 2015 15:18

Nguyễn Thị Loan

Trong thiết kế ASIC, trạng thái metastable là trạng thái mà tại thời điểm đó, giá trị của mạch không xác định được mức logic “0” hay “1”. Điều này dẫn đến hoạt động của mạch là không đoán trước được và có thể dẫn đến việc toàn bộ hệ thống bị sai Trong thiết kế ASIC, trạng thái metastable là trạng thái mà tại thời điểm đó, giá trị của mạch không xác định được mức logic “0” hay “1”. Điều này dẫn đến hoạt động của mạch là không đoán trước được và có thể dẫn đến việc toàn bộ hệ thống bị sai

Read more...

Phân biệt vi điều khiển - CPLD - FPGA

Monday, 13 July 2015 15:09

administrator

FPGA là gì? FPGA là chip lô-gic số lập trình được. Nghĩa là bạn có thể sử dụng chúng để lập trình hầu hết các chức năng của bất cứ mạng số nào.

Last Updated ( Wednesday, 17 October 2018 18:22 )

Read more...

Tìm hiểu về Field-Programmable Gate Array (FPGA)

Saturday, 11 July 2015 14:22

Nguyễn Thị Loan

Field-programmable gate array (FPGA) là một loại mạch tích hợp cỡ lớn dùng cấu trúc mảng phần tử logic mà người dùng có thể lập trình được.

Last Updated ( Friday, 28 September 2018 17:47 )

Read more...

Bảng một số thuật ngữ trong VLSI (Glossary)

Saturday, 11 July 2015 08:55

Nguyễn Thị Loan

Bảng một số thuật ngữ trong VLSI (Glossary)

Last Updated ( Monday, 29 April 2019 20:31 )

Read more...

Tham khảo kiến trúc clock của MSP430

Friday, 10 July 2015 15:35

Nguyễn Thị Loan

Mời các bạn tham khảo kiến trúc clock của dòng chip MSP430 Mời các bạn tham khảo kiến trúc clock của dòng chip MSP430

Last Updated ( Friday, 10 July 2015 15:55 )

Read more...

Quy trình thiết kế IP trong FPGA

Thursday, 09 July 2015 15:03

administrator

1. Định nghĩa về tài sản trí tuệ (Intellectual Property) Định nghĩa chung về IP: Tài sản trí tuệ là sản phẩm tạo ra bằng trí óc, ví dụ như các phát minh, sáng tác văn học và nghệ thuật, các thiết kế, biểu tượng, tên gọi và hình ảnh dùng trong thương mại.

Last Updated ( Thursday, 11 July 2019 18:36 )

Read more...

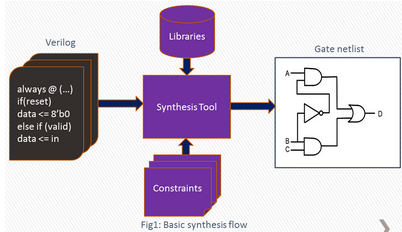

Quá trình tổng hợp (synthesis) trong thiết kế ASIC

Thursday, 09 July 2015 15:03

Nguyễn Thị Loan

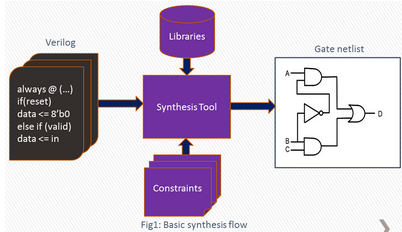

Thế nào là tổng hợp trong thiết kế ASIC. Thế nào là tổng hợp trong thiết kế ASIC. Synthesis (tổng hợp) là quá trình chuyển đổi từ dạng ngôn ngử mô tả ở mức cao thành dạng mức cổng

Last Updated ( Thursday, 09 July 2015 15:13 )

Read more...

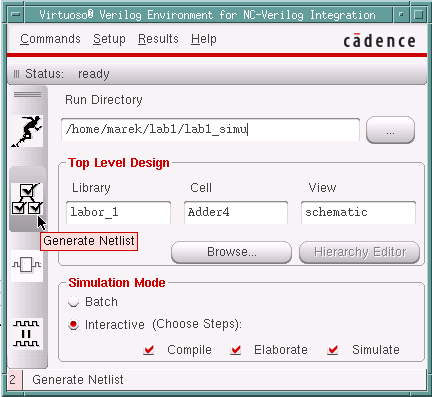

Giới thiệu sơ lược về các công cụ mô phỏng trong thiết kế ASIC

Thursday, 09 July 2015 13:49

Nguyễn Thị Loan

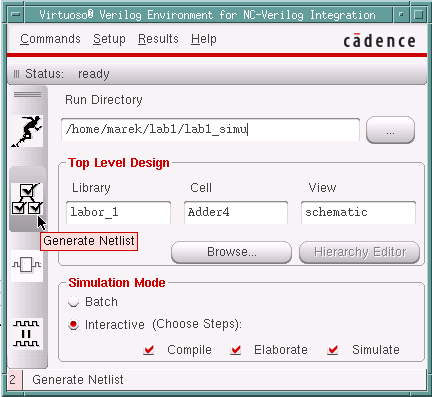

Công cụ mô phỏng (simulator)

Last Updated ( Thursday, 25 April 2019 20:00 )

Read more...

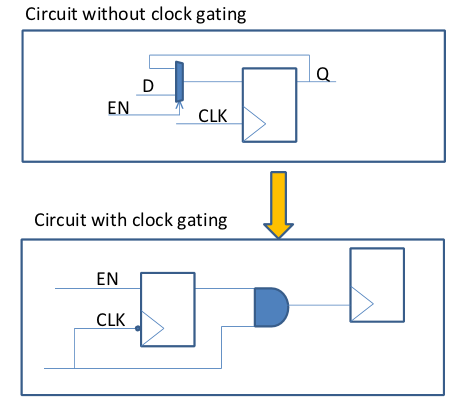

Thiết kế ASIC với mức năng lượng tiêu hao thấp (low power design)

Wednesday, 08 July 2015 19:37

Nguyễn Thị Loan

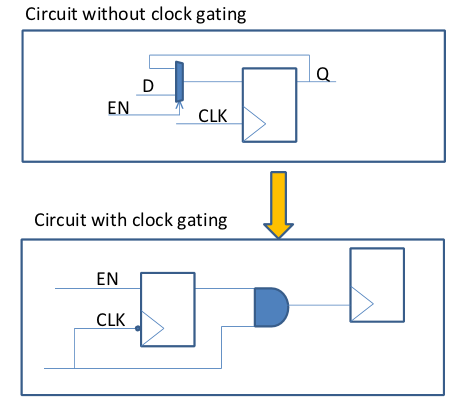

Vấn đề tiết kiệm năng lượng (low power consumption) Vấn đề tiết kiệm năng lượng (low power consumption)

Vần đề tiết kiệm năng lượng ngày nay luôn được xem là một vấn đề lớn trong bất kì sản phẩm thiết bị cầm tay nào (handset).

Last Updated ( Wednesday, 08 July 2015 20:01 )

Read more...

Tìm hiểu về SystemVerilog Assertion

Wednesday, 08 July 2015 13:55

Nguyễn Thị Loan

Verilog assertion có nhiều điểm hạn chế do bản thân ngôn ngữ không hỗ trợ trực tiếp việc viết Assertion mà phải thông qua các thư viện OVL hoặc PSL. Verilog assertion có nhiều điểm hạn chế do bản thân ngôn ngữ không hỗ trợ trực tiếp việc viết Assertion mà phải thông qua các thư viện OVL hoặc PSL.

Last Updated ( Monday, 20 July 2015 19:13 )

Read more...

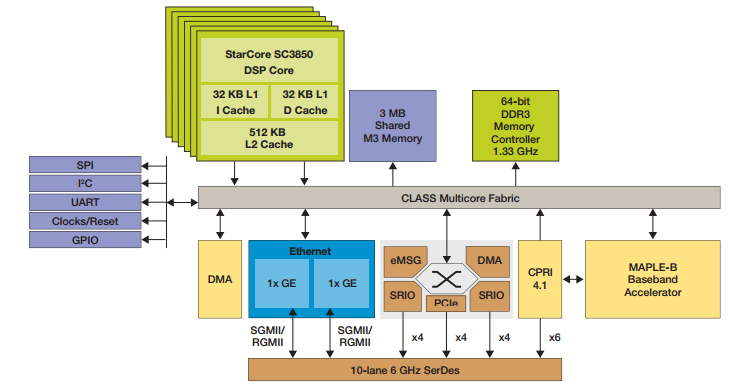

Tìm hiểu về kiến trúc của System on Chip (SoC)

Tuesday, 07 July 2015 15:43

1. Định nghĩa về SoC System on Chip là hệ thống mạch tích hợp bao gồm tất cả các thành phần cần thiết được tích hợp trên 1 chip duy nhất. Các thành phần này có thể bao gồm mạch số (digital), mạch analog và sự pha trộn giữa hai mạch này (mixed-signal)

Read more...

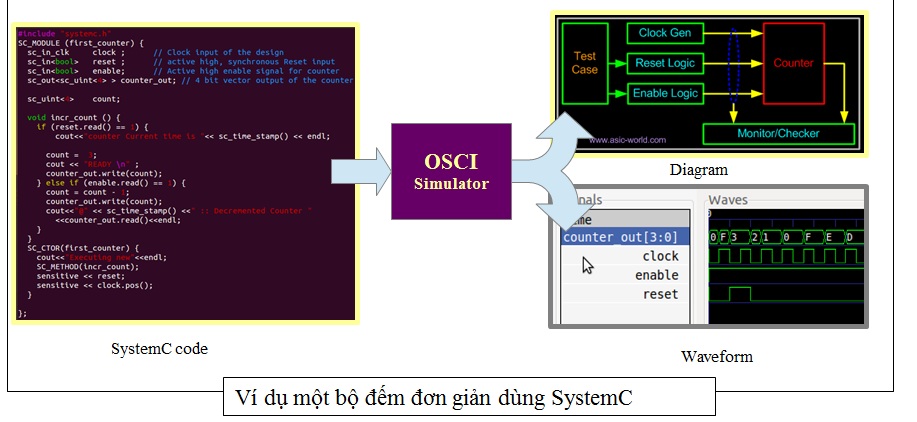

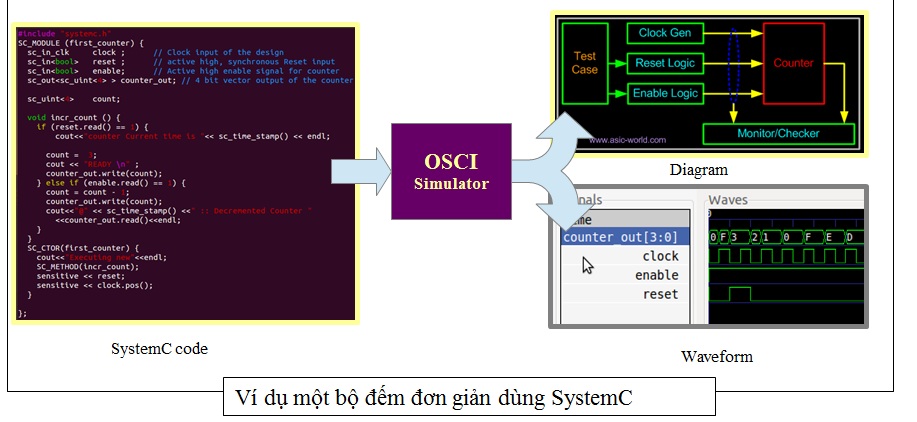

Ứng dụng của SystemC trong thiết kế phần cứng

Tuesday, 07 July 2015 15:37

Nguyễn Thị Loan

Tại sao cần phải sử dụng SystemC và vai trò của SystemC trong thiết kế phần cứng là gì? Câu trả lời có thể có được thông qua một ví dụ đơn giản như sau:

Last Updated ( Tuesday, 16 October 2018 21:02 )

Read more...

Sử dụng hàm random trong verilog

Tuesday, 07 July 2015 15:27

Hàm random được sử dụng để tạo ra các giá trị ngẫu nhiên. Mục đích của hàm random có thể được sử dụng để cho quá trình kiểm tra thiết kế một cách ngẫu nhiên, bằng cách đưa vào các input ngẫu nhiên. Ví dụ sử dụng hàm random để tạo address và data ngẫu nhiên như sau sau:

Last Updated ( Monday, 20 July 2015 19:14 )

Read more...

Giới thiệu sơ lược về các công cụ mô phỏng trong thiết kế ASIC

Tuesday, 07 July 2015 14:32

Nguyễn Thị Loan

Công cụ mô phỏng (simulator) Công cụ mô phỏng (simulator)

Trong sơ đồ thiết kế ASIC, ứng với mỗi công đoạn thiết, các kỹ sư thiết kế sẽ dùng các công cụ mô phỏng tướng ứng.

Last Updated ( Tuesday, 07 July 2015 20:08 )

Read more...

Mạch trừ

Tuesday, 07 July 2015 14:25

![[IMG]](http://huongnghiepviet.com/codientu/ki_thuat_cdt/dien_tu/vi_mach_so/chuong_2/images_c2/h23THbang.gif) .1 Mạch trừ nửa và trừ đủCũng gồm 2 loại mạch trừ nửa hay chưa đủ : haft subtractor (HS) và trừ đủ hay còn gọi là trừ bán phần : full subtractor (FS) (khi này cần bit mượn Bi trước tham gia vào phép tính) .1 Mạch trừ nửa và trừ đủCũng gồm 2 loại mạch trừ nửa hay chưa đủ : haft subtractor (HS) và trừ đủ hay còn gọi là trừ bán phần : full subtractor (FS) (khi này cần bit mượn Bi trước tham gia vào phép tính)

Read more...

|

|

|

|

|

|

|

Page 106 of 118 |

Trong thiết kế ASIC, trạng thái metastable là trạng thái mà tại thời điểm đó, giá trị của mạch không xác định được mức logic “0” hay “1”. Điều này dẫn đến hoạt động của mạch là không đoán trước được và có thể dẫn đến việc toàn bộ hệ thống bị sai

Trong thiết kế ASIC, trạng thái metastable là trạng thái mà tại thời điểm đó, giá trị của mạch không xác định được mức logic “0” hay “1”. Điều này dẫn đến hoạt động của mạch là không đoán trước được và có thể dẫn đến việc toàn bộ hệ thống bị sai

Mời các bạn tham khảo

Mời các bạn tham khảo Thế nào là tổng hợp trong thiết kế ASIC.

Thế nào là tổng hợp trong thiết kế ASIC.

Vấn đề tiết kiệm năng lượng (low power consumption)

Vấn đề tiết kiệm năng lượng (low power consumption) Verilog

Verilog

Công cụ mô phỏng (simulator)

Công cụ mô phỏng (simulator)![[IMG]](http://huongnghiepviet.com/codientu/ki_thuat_cdt/dien_tu/vi_mach_so/chuong_2/images_c2/h23THbang.gif) .1 Mạch trừ nửa và trừ đủ

.1 Mạch trừ nửa và trừ đủ