Video những vi mạch điện tử

Monday, 06 July 2015 14:19

Cùng tìm hiểu nha khi bạn muốn biết về chúng. Cùng tìm hiểu nha khi bạn muốn biết về chúng.

Video lập trình vi điều khiển

Sunday, 05 July 2015 13:45

Lập trình vi điều khiển-Phần 1-Giới thiệu mạch Arduino

Last Updated ( Tuesday, 07 July 2015 19:15 )

Read more...

video tư duy lập trình,nền tảng lập c, c++...

Saturday, 04 July 2015 14:51

Video Tư Duy Lập Trình, nền tảng lập trình C, C++, C#, Java, Javascript, PHP, ASP, ASP.NET.

Last Updated ( Tuesday, 07 July 2015 19:14 )

Read more...

FPGA làm việc như thế nào??

Friday, 03 July 2015 14:54

*Cấu trúc cơ bản của FPGA *Cấu trúc cơ bản của FPGA

- Fpga đươc cấu tạo cơ bản từ những khối logic (logic blocks), tùy vào loại FPGA mà nó có thể chứa từ hang tram đến hàng chục nghìn khối logic đươc bố trí dưới dạng ma trận. Mối khối logic chứa các LUT, 1 D-flipflop và 1 khối chọn kênh từ 2 sang một 2-to-1 mux.

Last Updated ( Friday, 07 August 2015 19:19 )

Read more...

Giới thiệu bộ xử lý ARM Cortex-M3

Thursday, 02 July 2015 15:01

1. Giới thiệu Giải pháp Soc (System-on-chip) dựa trên bộ vi xử lý nhúng ARM được ứng dụng vào rất nhiều thị trường khác nhau bao gồm các ứng dụng doanh nghiệp, các hệ thống ô tô, mạng gia đình và công nghệ mạng không dây...

Last Updated ( Thursday, 02 July 2015 16:05 )

Read more...

Đồng hồ báo thức sử dụng vi điều khiển 89S51

Wednesday, 01 July 2015 18:44

Đồng hồ báo thức là một chiếc đồng hồ mà chỉ một thời gian định trước bằng cách tạo ra âm thanh vào thời điểm đó. Chức năng này được sử dụng để đánh thức mọi người hay nhắc nhở họ về một điều gì đó Đồng hồ báo thức là một chiếc đồng hồ mà chỉ một thời gian định trước bằng cách tạo ra âm thanh vào thời điểm đó. Chức năng này được sử dụng để đánh thức mọi người hay nhắc nhở họ về một điều gì đó

Read more...

Hướng dẫn sử dụng phần mềm ModelSim

Tuesday, 30 June 2015 16:44

Chạy chương trình từ shortcut trên Desktop của máy tính hoặc vào menu Start → All Programs → ModelSim PE Student Edition → ModelSim, sau đó chờ chương trình khởi động.

Read more...

Hệ thống trên một vi mạch (SOC)

Sunday, 28 June 2015 11:38

Hệ thống trên một vi mạch (trong tiếng Anh gọi là system-on-a-chip, viết tắt là SoC hay SOC) là một hệ thống điện tử được xây dựng trên một đế silicon với ý tưởng ban đầu là tích hợp tất cả các thành phần của một hệ thống máy tính lên trên một vi mạch đơn (hay còn gọi là một chip đơn). Hệ thống SoC này có thể bao gồm các khối chức năng số, tương tự, tín hiệu kết hợp (mixed-signal) và cả các khối tần số radio (RF). Ứng dụng điển hình của các hệ thống trên một vi mạch là các hệ thống nhúng. Hệ thống trên một vi mạch (trong tiếng Anh gọi là system-on-a-chip, viết tắt là SoC hay SOC) là một hệ thống điện tử được xây dựng trên một đế silicon với ý tưởng ban đầu là tích hợp tất cả các thành phần của một hệ thống máy tính lên trên một vi mạch đơn (hay còn gọi là một chip đơn). Hệ thống SoC này có thể bao gồm các khối chức năng số, tương tự, tín hiệu kết hợp (mixed-signal) và cả các khối tần số radio (RF). Ứng dụng điển hình của các hệ thống trên một vi mạch là các hệ thống nhúng.

Read more...

Giới thiệu về ngôn ngữ verilog

Friday, 26 June 2015 18:55

1,Giới thiệu 1,Giới thiệu

-- Verilog là ngôn ngữ mô tả phần cứng (Hardware Description Language)được sử dụng trong việc thiết kế các các hệ thống số, các mạch tích hợp: như bộ nhớ RAM, bộ vi xử lý hoặc đơn giản là

Last Updated ( Monday, 20 July 2015 19:15 )

Read more...

Hướng dẫn cách đếm chân ic đơn giản

Friday, 26 June 2015 16:37

Với ic chúng ta không có cách nào có thể xác định chân như tranzitor được cách duy nhất là phải biết cách đếm chân của ic để tiện lắp mạch điện tử . Ví dụ: Với ic 2025 (ic công suất âm tần mình sẽ nói chức năng con này sau) Với ic chúng ta không có cách nào có thể xác định chân như tranzitor được cách duy nhất là phải biết cách đếm chân của ic để tiện lắp mạch điện tử . Ví dụ: Với ic 2025 (ic công suất âm tần mình sẽ nói chức năng con này sau)

Read more...

Hướng dẫn làm mạch sạc điện thoại dự phòng từ ac quy V2 bằng TIP41 hoặc D718

Friday, 26 June 2015 16:13

Hôm nay mình hướng dẫn các bạn 1 tác phẩm sạc v2 kinh điển hơn và cũng rất đơn giản nhưng sẽ giải quyết tất cả vấn đề sạc quá chậm, không nhận sạc... Hôm nay mình hướng dẫn các bạn 1 tác phẩm sạc v2 kinh điển hơn và cũng rất đơn giản nhưng sẽ giải quyết tất cả vấn đề sạc quá chậm, không nhận sạc...

Read more...

Thiết Kế Verilog cho Bộ mã hóa ưu tiên!

Wednesday, 24 June 2015 15:48

Bộ Mã Hóa sử dụng diễn tả IF 1 //----------------------------------------------------- 2 // Design Name : encoder_using_if 3 // File Name : encoder_using_if.v 4 // Function : Encoder using If

Read more...

Thiết Kế Verilog cho Verilog - FIFO bất đồng bộ!

Wednesday, 24 June 2015 15:26

FIFO is an acronym for First In, First Out, an abstraction in ways of organizing and manipulation of data relative to time and prioritization. This expression describes the principle of a queue processing technique or servicing conflicting demands by ordering process by first-come, first-served (FCFS) behaviour: what comes in first is handled first, what comes in next waits until the first is finished, etc.

Last Updated ( Monday, 20 July 2015 19:16 )

Read more...

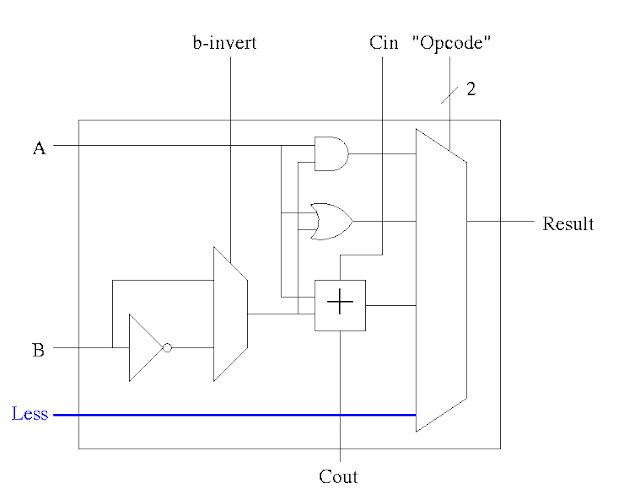

ALU Design

Saturday, 20 June 2015 09:16

administrator

Mục tiêu đầu tiên là thiết kế ALU 32-bit có thực hiện phép toán AND, OR và cộng. Đầu tiên để hiểu rõ được những điều dưới đây bạn cần hiểu ALU là gì ?

Last Updated ( Thursday, 18 October 2018 19:20 )

Read more...

Lập trình I/O trên thẻ nhớ

Friday, 19 June 2015 20:58

Hiện nay, hệ thống file FAT (DOS) được lấy làm chuẩn định dạng cho thẻ nhớ flash. Bạn có thể dùng một con vi điều khiển để đọc và ghi file trên một thẻ nhớ SD hay MMC với hệ thống FAT. Hiện nay, hệ thống file FAT (DOS) được lấy làm chuẩn định dạng cho thẻ nhớ flash. Bạn có thể dùng một con vi điều khiển để đọc và ghi file trên một thẻ nhớ SD hay MMC với hệ thống FAT.

Read more...

|

|

![[IMG]](https://lh3.googleusercontent.com/--MdnfliWg1Q/VSAMGd50X-I/AAAAAAAACHw/WxvNWEY2eyk/w342-h318-no/t%E1%BA%A3i%2Bxu%E1%BB%91ng.png)

Cùng tìm hiểu nha khi bạn muốn biết về chúng.

Cùng tìm hiểu nha khi bạn muốn biết về chúng.

*Cấu trúc cơ bản của FPGA

*Cấu trúc cơ bản của FPGA

Với ic chúng ta không có cách nào có thể xác định chân như tranzitor được cách duy nhất là phải biết cách đếm chân của ic để tiện lắp mạch điện tử . Ví dụ: Với ic 2025 (ic công suất âm tần mình sẽ nói chức năng con này sau)

Với ic chúng ta không có cách nào có thể xác định chân như tranzitor được cách duy nhất là phải biết cách đếm chân của ic để tiện lắp mạch điện tử . Ví dụ: Với ic 2025 (ic công suất âm tần mình sẽ nói chức năng con này sau) Hôm nay mình hướng dẫn các bạn 1 tác phẩm sạc v2 kinh điển hơn và cũng rất đơn giản nhưng sẽ giải quyết tất cả vấn đề

Hôm nay mình hướng dẫn các bạn 1 tác phẩm sạc v2 kinh điển hơn và cũng rất đơn giản nhưng sẽ giải quyết tất cả vấn đề